### **Code Generation**

1

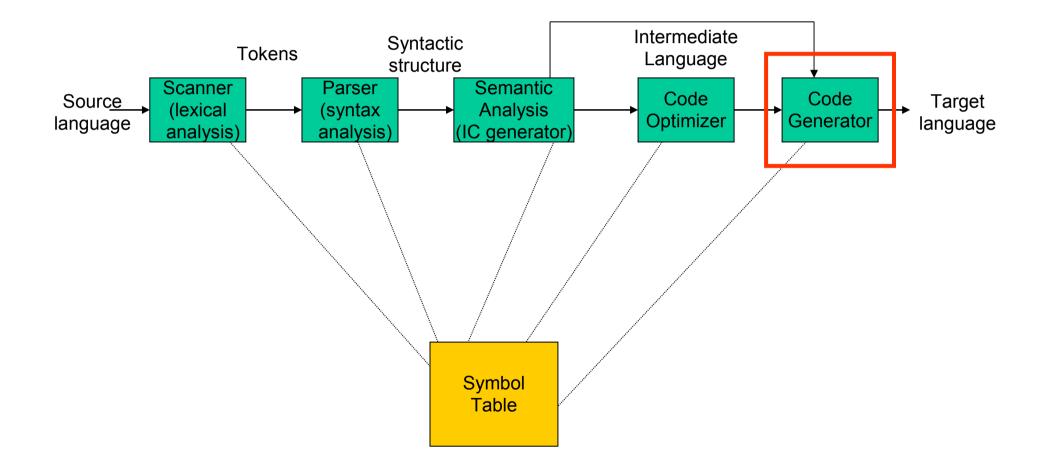

### **Compiler Architecture**

## **Code Generation**

- The code generation problem is the task of mapping intermediate code to machine code

- Machine Dependent Optimization

- Requirements:

- Correctness

- Efficiency

#### Issues

- Input language: intermediate code (optimized or not)

- Target architecture: must be **well** understood

- Interplay between

- Instruction Selection

- Register Allocation

- Instruction Scheduling

#### Example Target: MIPS Assembly Language

- General Characteristics

- Byte-addressable with 4-byte words

- N general-purpose registers

- Three-address instructions: op destination, source1, source2

| 0  | zer | o constant 0            | 16 | <b>s0</b> | callee saves           |

|----|-----|-------------------------|----|-----------|------------------------|

| 1  | at  | reserved for assembler  |    | (cal      | ler can clobber)       |

| 2  | v0  | expression evaluation & | 23 | s7        |                        |

| 3  | v1  | function results        | 24 | <b>t8</b> | temporary (cont'd)     |

| 4  | a0  | arguments               | 25 | <b>t9</b> |                        |

| 5  | a1  |                         | 26 | k0        | reserved for OS kernel |

| 6  | a2  |                         | 27 | k1        |                        |

| 7  | a3  |                         | 28 | gp        | Pointer to global area |

| 8  | t0  | temporary: caller saves | 29 | sp        | Stack pointer          |

|    |     | (callee can clobber)    | 30 | fp        | frame pointer          |

| 15 | t7  |                         | 31 | ra        | Return Address (HW)    |

## Instruction Selection

- There may be a large number of 'candidate' machine instructions for a given IC instruction

- each has own cost and constraints

- cost may be influenced by surrounding context

- different architectures have different needs that must be considered: speed, power constraints, space ...

## Instruction Scheduling

- Choosing the order of instructions to best utilize resources

- Architecture

- -RISC (pipeline)

- Vector processing

- Superscalar and VLIW

- Memory hierarchy

- Ordering to decrease memory fetching

- Latency tolerance doing something when data does have to be fetched

## **Register Allocation**

- How to best use the bounded number of registers

- Complications:

- Special purpose registers

- Operators requiring multiple registers

#### Naive Approach to Code Generation

- Simple code generation algorithm:

- Define a target code sequence for each intermediate code statement type

- Why is this not sufficient?

# Mapping from Intermediate Code

- Simple code generation algorithm:

- Define a target code sequence to each intermediate code statement type

| Intermediate | becomes                                                                     | Intermediate | becomes                                                                     |

|--------------|-----------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------|

| a := b       | lw \$t0,b<br>sw \$t0,a                                                      | a := b + c   | lw \$t0,b<br>lw \$t1,c<br>add \$t0,\$t0,\$t1<br>sw \$t0,a                   |

| a := b[c]    | la \$t0,b<br>lw \$t1,c<br>add \$t0,\$t0,\$t1<br>lw \$t0,(\$t0)<br>sw \$t0,a | a[b] := c    | la \$t0,a<br>lw \$t1,b<br>add \$t0,\$t0,\$t1<br>lw \$t1,c<br>sw \$t1,(\$t0) |

## Mapping from Intermediate Code

Consider the C statement: a[i] = d[c[k]];

| t1 := 4 * k  | lw \$t0,k<br>sll \$t0,\$t0,2                       | t4 := d[t3] | la \$t0,d<br>lw \$t1,t3                                     |

|--------------|----------------------------------------------------|-------------|-------------------------------------------------------------|

| t2 := c[t1]  | sw \$t0,t1<br>la \$t0,c<br>lw \$t1,t1              |             | add \$t0,\$t0,\$t1<br>lw \$t0,(\$t0)<br>sw \$t0,t4          |

|              | add \$t0,\$t0,\$t1<br>lw \$t0,(\$t0)<br>sw \$t0,t2 | t5 := 4 * i | lw \$t0,i<br>sll \$t0,\$t0,2<br>sw \$t0,t5                  |

| t3 := 4 * t2 | lw \$t0,t2<br>sll \$t0,\$t0,2<br>sw \$t0,t3        | a[t5] := t4 | la \$t0,a<br>lw \$t1,t5<br>add \$t0,\$t0,\$t1<br>lw \$t1,t4 |

|              |                                                    |             | sw \$t1,(\$t0)                                              |

We use 24 instructions (18 load/store + 6 arithmetic) and allocate space for five temporaries (but only use two registers).

## Problems with this approach

- Local decisions do not produce good code

- Does not take temporary variables into account

- Get rid of the temporaries (reduce load/store):

a[i] = d[c[k]];

```

la $t0,c

lw $t1,k

sll $t1,$t1,2

add $t0,$t0,$t1 # address of c[k]

lw $t0,($t0)

la $t1,d

sll $t0,$t0,2

add $t1,$t1,$t0 # address of d[c[k]]

lw $t1,($t1)

la $t0,a

lw $t2,i

sll $t2,$t2,2

add $t0,$t0,$t2 # address of a[i]

sw $t1,($t0)

```

## How to Improve Quality

- Need a way to generate machine code based on past and future use of the data

- -Analyze the code

- -Use results of analysis

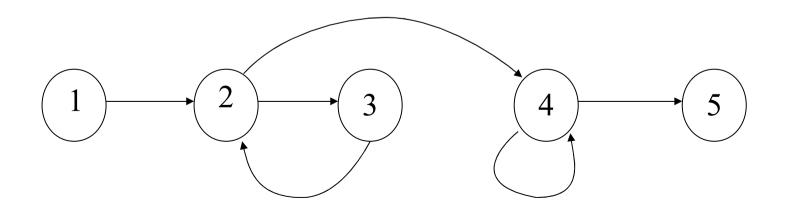

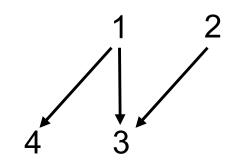

#### Representing Intermediate Code: Control Flow Graph - CFG

#### CFG = < V, E, Entry >, where

- V = vertices or nodes, representing an instruction or basic block (group of statements).

- $E = (V \times V)$  edges, potential flow of control

- Entry is an element of V, the unique program entry

## **Basic Blocks**

- A basic block is a sequence of consecutive statements with single entry/single exit:

- Flow of control only enters at the beginning

- Flow of control only leaves at the end

- Variants: single entry/multiple exit, multiple entry/single exit

# Generating CFGs from Intermediate Code

- Partition intermediate code into basic blocks

- Add edges corresponding to control flow between blocks

- Unconditional goto

- Conditional goto multiple edges

- No goto at end control passes to first statement of next block

## Partitioning into Basic Blocks

- Input: A sequence of intermediate code statements

- Determine the leaders, the first statements of basic blocks

- The first statement in the sequence is a leader

- Any statement that is the target of a goto (conditional or unconditional) is a leader

- Any statement immediately following a goto (conditional or unconditional) is a leader

- For each leader, its basic block is the leader and all statements up to, but not including, the next leader or the end of the program

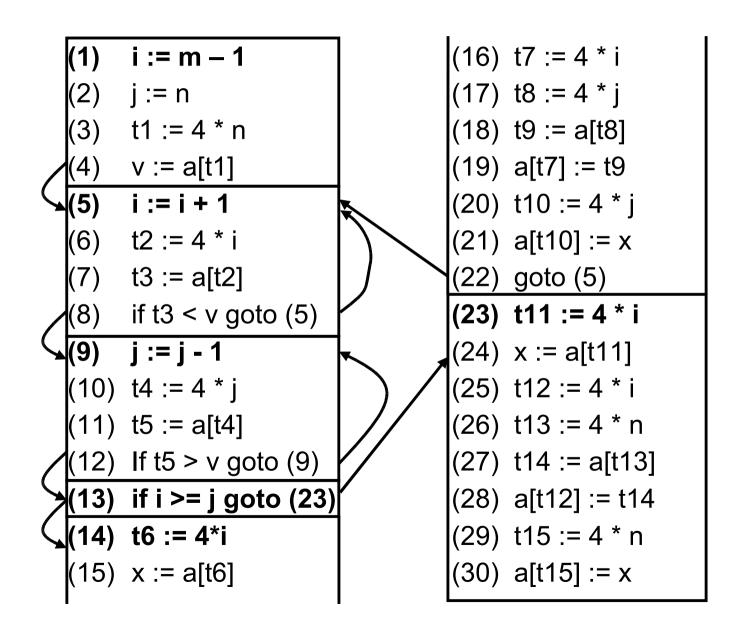

## Example Code

| i := m – 1          | (16)                                                                                                                                                                                                                        | t7 := 4 * i                                                                                                                                                                                                                                                          |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| j := n              | (17)                                                                                                                                                                                                                        | t8 := 4 * j                                                                                                                                                                                                                                                          |

| t1 := 4 * n         | (18)                                                                                                                                                                                                                        | t9 := a[t8]                                                                                                                                                                                                                                                          |

| v := a[t1]          | (19)                                                                                                                                                                                                                        | a[t7] := t9                                                                                                                                                                                                                                                          |

| i := i + 1          | (20)                                                                                                                                                                                                                        | t10 := 4 *                                                                                                                                                                                                                                                           |

| t2 := 4 * i         | (21)                                                                                                                                                                                                                        | a[t10] := x                                                                                                                                                                                                                                                          |

| t3 := a[t2]         | (22)                                                                                                                                                                                                                        | goto (5)                                                                                                                                                                                                                                                             |

| if t3 < v goto (5)  | (23)                                                                                                                                                                                                                        | t11 := 4 *                                                                                                                                                                                                                                                           |

| j := j - 1          | (24)                                                                                                                                                                                                                        | x := a[t11]                                                                                                                                                                                                                                                          |

| t4 := 4 * j         | (25)                                                                                                                                                                                                                        | t12 := 4 *                                                                                                                                                                                                                                                           |

| t5 := a[t4]         | (26)                                                                                                                                                                                                                        | t13 := 4 *                                                                                                                                                                                                                                                           |

| If t5 > v goto (9)  | (27)                                                                                                                                                                                                                        | t14 := a[t1                                                                                                                                                                                                                                                          |

| if i >= j goto (23) | (28)                                                                                                                                                                                                                        | a[t12] := t                                                                                                                                                                                                                                                          |

| t6 := 4*i           | (29)                                                                                                                                                                                                                        | t15 := 4 *                                                                                                                                                                                                                                                           |

| x := a[t6]          | (30)                                                                                                                                                                                                                        | a[t15] := x                                                                                                                                                                                                                                                          |

|                     | j := n<br>t1 := 4 * n<br>v := a[t1]<br>i := i + 1<br>t2 := 4 * i<br>t3 := a[t2]<br>if t3 < v  goto  (5)<br>j := j - 1<br>t4 := 4 * j<br>t5 := a[t4]<br>If t5 > v  goto  (9)<br>$if i \ge j \text{ goto } (23)$<br>t6 := 4*i | j := n(17) $t1 := 4 * n$ (18) $v := a[t1]$ (19) $i := i + 1$ (20) $t2 := 4 * i$ (21) $t3 := a[t2]$ (22) $if t3 < v  goto  (5)$ (23) $j := j - 1$ (24) $t4 := 4 * j$ (25) $t5 := a[t4]$ (26)If $t5 > v  goto  (9)$ (27) $if i >= j  goto  (23)$ (28) $t6 := 4*i$ (29) |

| (18) | t9 := a[t8]   |

|------|---------------|

| (19) | a[t7] := t9   |

| (20) | t10 := 4 * j  |

| (21) | a[t10] := x   |

| (22) | goto (5)      |

| (23) | t11 := 4 * i  |

| (24) | x := a[t11]   |

| (25) | t12 := 4 * i  |

| (26) | t13 := 4 * n  |

| (27) | t14 := a[t13] |

| (28) | a[t12] := t14 |

| (29) | t15 := 4 * n  |

| (30) | a[t15] := x   |

|      |               |

#### **Block Leaders**

| (1)  | i := m – 1          |

|------|---------------------|

| (2)  | j := n              |

| (3)  | t1 := 4 * n         |

| (4)  | v := a[t1]          |

| (5)  | i := i + 1          |

| (6)  | t2 := 4 * i         |

| (7)  | t3 := a[t2]         |

| (8)  | if t3 < v goto (5)  |

| (9)  | j := j - 1          |

| (10) | t4 := 4 * j         |

| (11) | t5 := a[t4]         |

| (12) | If t5 > v goto (9)  |

| (13) | if i >= j goto (23) |

| (14) | t6 := 4*i           |

| (15) | x := a[t6]          |

| (16) | t7 := 4 * i   |

|------|---------------|

| (17) | t8 := 4 * j   |

| (18) | t9 := a[t8]   |

| (19) | a[t7] := t9   |

| (20) | t10 := 4 * j  |

| (21) | a[t10] := x   |

| (22) | goto (5)      |

| (23) | t11 := 4 * i  |

| (24) | x := a[t11]   |

| (25) | t12 := 4 * i  |

| (26) | t13 := 4 * n  |

| (27) | t14 := a[t13] |

| (28) | a[t12] := t14 |

| (29) | t15 := 4 * n  |

| (30) | a[t15] := x   |

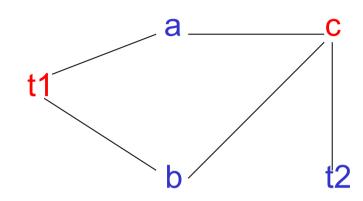

#### Flow Graph

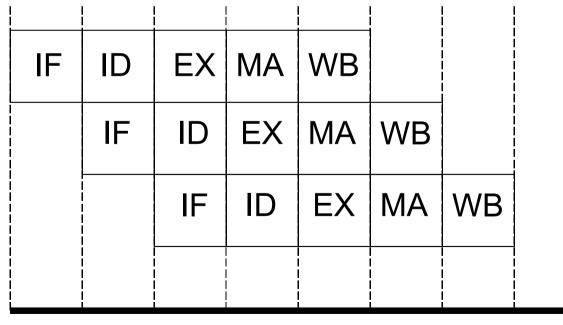

## Instruction Scheduling

- Choosing the order of instructions to best utilize resources (CPU, registers, ...)

- Consider RISC pipeline architecture:

IF – Instruction Fetch

- ID Instruction Decode

- EX Execute

- MA Memory access

- WB Write back

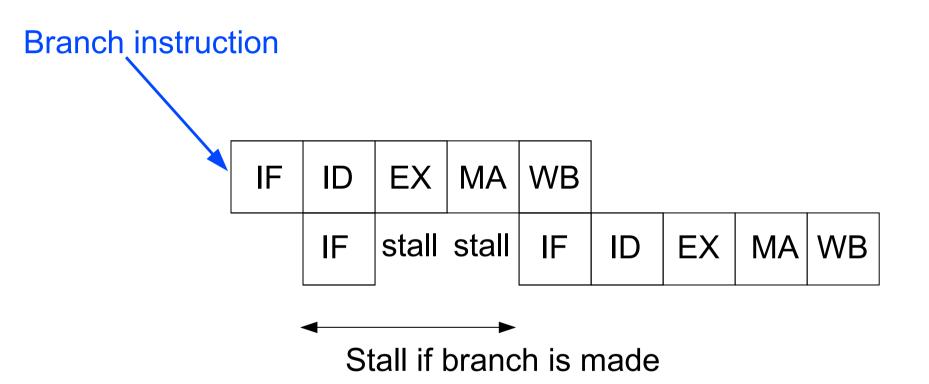

### Hazards

- 1. Structural hazards machine resources limit overlap

- 2. Data hazards output of instruction needed by later instruction

- 3. Control hazards branching

Pipeline stalls!

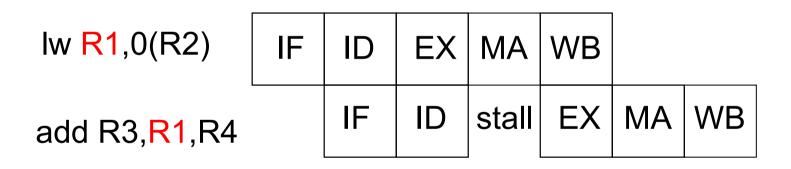

#### Data Hazards

Memory latency:

Can't add until register R1 is loaded.

#### **Structural Hazards**

Instruction latency:

#### Assumes floating point ops take 2 execute cycles

## **Dealing with Data Hazards**

- Typical solution is to re-order statements

- To do this without changing the outcome, need to understand the relationship (dependences) between statements

| addf R3,R1,R2 | IF | ID | EX | EX | MA | WB |    |    |

|---------------|----|----|----|----|----|----|----|----|

| add R5,R5,R6  |    | IF | ID | EX | MA | WB |    |    |

| addf R3,R3,R4 |    |    | IF | ID | EX | EX | MA | WB |

## Instruction Scheduling

- Many operations have non-zero latencies

- Execution time is *order-dependent*

- Assumed latencies (conservative):

| <b>Operation</b> | <u>Cycles</u> |

|------------------|---------------|

| load             | 3             |

| store            | 3             |

| loadl            | 1             |

| add              | 1             |

| mult             | 2             |

| fadd             | 1             |

| fmult            | 2             |

| shift            | 1             |

| branch           | 0 to 8        |

### $w \leftarrow w * 2 * x * y * z$

| •   | Schedul    | e 1            |          | •   | Schedul   | e 2            |

|-----|------------|----------------|----------|-----|-----------|----------------|

| 1   | lw         | \$t0,w         |          | 1   | lw        | \$t0,w         |

| 4   | add        | \$t0,\$t0,\$t0 |          | 2   | lw        | \$t1,x         |

| 5   | lw         | \$t1,x         |          | 3   | lw        | \$t2,y         |

| 8   | mult       | \$t0,\$t0,\$t1 |          | 4   | add       | \$t0,\$t0,\$t0 |

| 9   | lw         | \$t1,y         |          | 5   | mult      | \$t0,\$t0,\$t1 |

| 12  | mult       | \$t0,\$t0,\$t1 |          | 6   | lw        | \$t1,z         |

| 13  | lw         | \$t1,z         |          | 7   | mult      | \$t0,\$t0,\$t2 |

| 16  | mult       | \$t0,\$t0,\$t1 |          | 9   | mult      | \$t0,\$t0,\$t1 |

| 18  | SW         | \$t0,w         |          | 11  | SW        | \$t0,w         |

|     |            |                |          |     |           |                |

| dor | ne at time | 21             | _ /      | don | e at time | 14             |

|     |            | Is             | sue time |     |           |                |

#### **Control Hazards**

# **Branch Scheduling**

- Problem:

- Branches often take some number of cycles to complete, creating delay slots

- Can be a delay between a compare b and its associated branch

- Even unconditional branches have delay slots

- A compiler will try to fill these delay slots with valid instructions (rather than nop)

## Example

- Assume loads take 2 cycles and branches have a delay slot

- 7 cycles

- Can look at the dependencies between the statements and move a statement into the delay slot

| Instruction          | Start Time |

|----------------------|------------|

| lw \$t2,4(\$t1)      | 1          |

| lw \$t3,8(\$t1)      | 2          |

| add \$t4, \$t2, \$t3 | 4          |

| add \$t5, \$t2,1     | 5          |

| b L1                 | 6          |

| nop                  | 7          |

## Example

5 cycles filling delay slots

| Instruction          | Start Time |

|----------------------|------------|

| lw \$t2,4(\$t1)      | 1          |

| lw \$t3,8(\$t1)      | 2          |

| add \$t5, \$t2,1     | 3          |

| bL1                  | 4          |

| add \$t4, \$t2, \$t3 | 5          |

## **Register Allocation**

How to best use the bounded number of registers.

- Reducing load/store operations

- What are best values to keep in registers?

- When can we 'free' registers?

Complications:

- special purpose registers

- operators requiring multiple registers

## **Register Allocation Algorithms**

- Local (basic block level):

- Basic using liveness information

- Register Allocation using graph coloring

- Global (CFG)

- Need to use global liveness information

## **Basic Code Generation**

- Deal with each basic block individually

- Compute liveness information for the block

- Using liveness information, generate code that uses registers as well as possible

- At end, generate code that saves any live values left in registers

## **Concept: Variable Liveness**

- For some statement *s*, variable *x* is **live** if

- there is a statement *t* that uses *x*

- there is a path in the CFG from *s* to *t*

- there is no assignment to *x* on some path from *s* to *t*

- A variable is *live* at a given point in the source code if it could be used before it is defined

- Liveness tells us whether we care about the value held by a variable

#### Example: When Is a Live?

a := b + c

t1 := a \* a b := t1 + a c := t1 \* b

t2 := c + b

a := t2 + t2

Assume a,b and c are used after this basic block

#### Example: When Is b Live?

a := b + c t1 := a \* a b := t1 + a c := t1 \* b t2 := c + b a := t2 + t2

Assume a,b and c are used after this basic block

# Computing Live Status in Basic Blocks

- Input: A basic block

- Output: For each statement, set of variables live after the statement

- Initially all non-temporary variables go into live set (L)

- for i = *last* statement to *first* statement:

For statement i: x := y op z

- 1. Attach L to statement i

- 2. Remove x from set L

- 3. Add y and z to set L

|              | live = {}      |

|--------------|----------------|

| a := b + c   | live = {}      |

| t1 := a * a  | ₩C – ſ         |

| 1 14 .       | live = {}      |

| b := t1 + a  | live = {}      |

| c := t1 * b  |                |

| t2 := a + b  | live = {}      |

| t2 := c + b  | live = {}      |

| a := t2 + t2 |                |

|              | live = {a,b,c} |

|              | live = {}                     |

|--------------|-------------------------------|

| a := b + c   | live = {}                     |

| t1 := a * a  |                               |

| b := t1 + a  | live = {}                     |

| - 14 + 1-    | live = {}                     |

| c := t1 * b  | live = {}                     |

| t2 := c + b  |                               |

| a := t2 + t2 | live = {b,c,t2}               |

|              | live = { <mark>a</mark> ,b,c} |

|              | live = {}                   |

|--------------|-----------------------------|

| a := b + c   |                             |

| t1 := a * a  | live = {}                   |

|              | live = {}                   |

| b := t1 + a  |                             |

| c := t1 * b  | live = {}                   |

| 011 0        | live = { <mark>b,c</mark> } |

| t2 := c + b  |                             |

| a := t2 + t2 | live = $\{b,c,t2\}$         |

| a .– IZ + IZ | live = {a,b,c}              |

|              |                             |

|                    | live = {}                   |

|--------------------|-----------------------------|

| a := b + c         | live = {}                   |

| t1 := a * a        |                             |

| b := t1 + a        | live = {}                   |

| o +1 * b           | live = {b,t1}               |

| <b>c</b> := t1 * b | live = {b, <mark>c</mark> } |

| t2 := c + b        | live = {b,c,t2}             |

| a := t2 + t2       | πνο – <sub>τ</sub> ο,ο,ιΖ}  |

|                    | live = {a,b,c}              |

| _                        | live = {}                    |

|--------------------------|------------------------------|

| a := b + c               | live = {}                    |

| t1 := a * a              | live = {a,t1}                |

| <mark>b</mark> := t1 + a |                              |

| a 1- +1 * h              | live = { <mark>b</mark> ,t1} |

| c := t1 * b              | live = {b,c}                 |

| t2 := c + b              |                              |

| a := t2 + t2             | live = $\{b,c,t2\}$          |

| a .– IZ + IZ             | live = {a,b,c}               |

|              | live = {}                    |

|--------------|------------------------------|

| a := b + c   | live = {a}                   |

| t1 := a * a  | πνς – τ <mark>α</mark> λ     |

| 1 14 .       | live = {a, <mark>t1</mark> } |

| b := t1 + a  | live = $\{b,t1\}$            |

| c := t1 * b  |                              |

| t2 := c + b  | live = $\{b,c\}$             |

| 120+0        | live = $\{b,c,t2\}$          |

| a := t2 + t2 |                              |

|              | live = {a,b,c}               |

|              | live = { <mark>b,c</mark> } | $\leftarrow$ what does this mean? |

|--------------|-----------------------------|-----------------------------------|

| a := b + c   |                             |                                   |

| 14           | live = { <mark>a</mark> }   |                                   |

| t1 := a * a  | live = {a,t1}               |                                   |

| b := t1 + a  | πνο – <i>τ</i> α,ττζ        |                                   |

|              | live = {b,t1}               |                                   |

| c := t1 * b  |                             |                                   |

| +0 a + b     | live = {b,c}                |                                   |

| t2 := c + b  | live = $\{b,c,t2\}$         |                                   |

| a := t2 + t2 |                             |                                   |

|              | live = {a,b,c}              |                                   |

# **Basic Code Generation**

- Deal with each basic block individually

- Compute liveness information for the block

- Using liveness information, generate code that uses registers as well as possible

- At end, generate code that saves any live values left in registers

# **Basic Code Generation**

- Idea: Deal with the instructions from beginning to end. For each instruction,

- Use registers whenever possible

- A non-live value in a register can be discarded, freeing that register

- Data Structures:

- Register descriptor register status (empty, full) and contents (one or more "values")

- Address descriptor the location (or locations) where the current value for a variable can be found (register, stack, memory)

### Instruction type: $\mathbf{x} := \mathbf{y} \circ \mathbf{p} \mathbf{z}$

- Choose  $R_x$ , the register where the result (x) will be kept

- If y (or z) is the only variable in a register t and not live after the statement, choose  $R_x = t$

- Else if there is a free register t, choose  $R_x = t$

- Else must free up a register for  $R_x$

- Find R<sub>y</sub>. If y is not in a register, generate load into a free register (or R<sub>x</sub>)

- Find R<sub>z</sub>. If z is not in a register, generate load into a free register (can use R<sub>x</sub> if not used by y)

- Generate: OP R<sub>x</sub>, R<sub>y</sub>, R<sub>z</sub>

# Instruction type: $\mathbf{x} := \mathbf{y} \circ \mathbf{p} \mathbf{z}$

- Update information about the current location of x

- Update information for the register holding x

- If y and/or z are not live after this instruction, update register and address descriptors accordingly

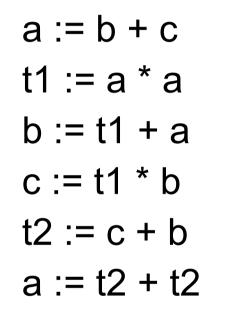

### Example Code

| _  |

|----|

| 2} |

| }  |

|    |

Initially

Three Registers: (-;-;-) all empty Current values: (a;b;c;t1;t2) = (m;m;m;-;-)

- Instruction 1: a := b + c, Live = {a}

R<sub>a</sub> = \$t0, R<sub>b</sub> = \$t0, R<sub>c</sub> = \$t1

- 1w \$t0,b

- lw \$t1,c

Don't need to keep track of b or c since aren't live.

• add \$t0,\$t0,\$t1 Registers: (a;-;-)

current values: (\$t0;-;-;-)

- Instruction 2: t1 := a \* a, Live = {a,t1}

R<sub>t1</sub> = \$t1 (since a is live after instruction)

mul \$t1,\$t0,\$t0

Registers: (a;t1;-)

- Instruction 3: b := t1 + a, Live = {b,t1} Since a is not live after instruction,  $R_b =$ \$t0

- add \$t0,\$t1,\$t0

Registers: (b;t1;-) current values: (-;\$t0;-;\$t1;-)

- Instruction 4: c := t1 \* b, Live = {b,c} Since t1 is not live after instruction, R<sub>c</sub> = \$t1 mul \$t1,\$t1,\$t0 Registers: (b;c;-) current values: (-;\$t0;\$t1;-;-)

- Instruction 5: t2 := c + b, Live = {b,c,t2}

R<sub>t2</sub> = \$t2

- add \$t2,\$t1,\$t0

Registers: (b;c;t2)

current values: (-;\$t0;\$t1;-;\$t2)

Instruction 6: a := t2 + t2, Live = {a,b,c}

R<sub>a</sub> = \$t2

#### add \$t2,\$t2,\$t2

Registers: (b;c;a) current values: (\$t2;\$t0;\$t1;-;-)

- Since end of block, move live variables:

- sw \$t2,a

- sw \$t0,b

- sw \$t1,c

all registers available

all live variables moved to memory

### Generated code

- lw \$t0,b a := b + clw \$t1,c add \$t0,\$t0,\$t1 mul \$t1,\$t0,\$t0 t1 := a \* a add \$t0,\$t1,\$t0 b := t1 + a c := t1 \* b mul \$t1,\$t1,\$t0 t2 := c + b add \$t2,\$t1,\$t0 a := t2 + t2 add \$t2,\$t2,\$t2 sw \$t2,a sw \$t0,b sw \$t1,c

- Cost = 16 How does this compare to naive approach?

# Improving Efficiency

- Liveness information allows us to keep values in registers if they will be used later (efficiency)

- Why do we assume all variables are live at the end of blocks? Can we do better?

- Why do we need to save live variables at the end? We might have to reload them in the next block.

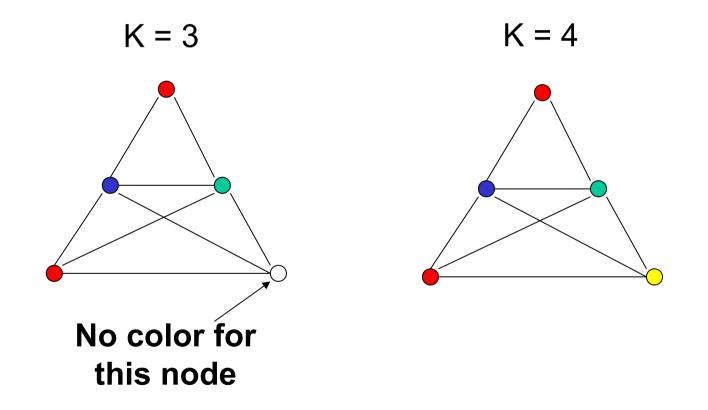

### Register Allocation with Graph Coloring

- Local register allocation graph coloring problem

- Uses liveness information

- Allocate K registers where each register is associated with one of the K colors

# Graph Coloring

- The coloring of a graph G = (V,E) is a mapping C:

V→ S, where S is a finite set of colors, such that if edge vw is in E, C(v) <> C(w)

- Problem is NP (for more than 2 colors) → no polynomial time solution

- Fortunately there are approximation algorithms

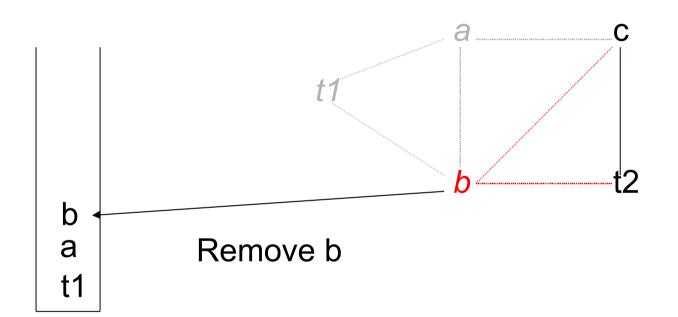

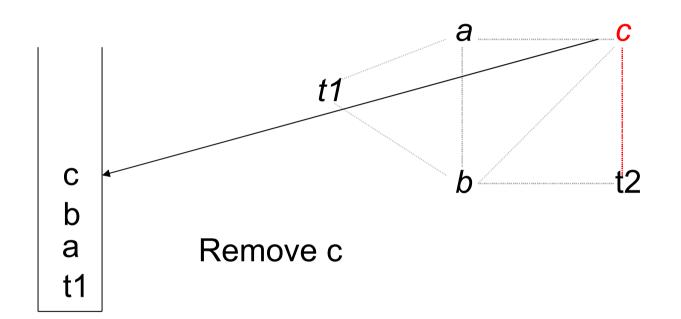

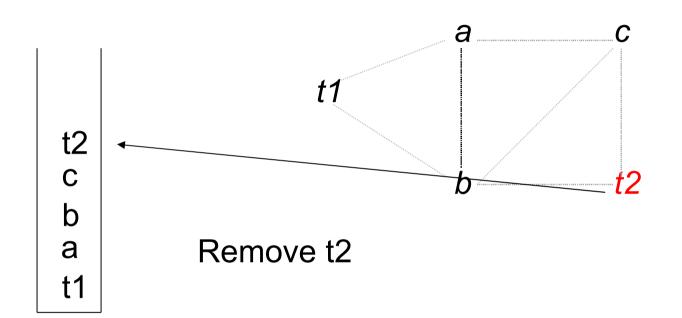

# Coloring a Graph with K Colors

### Register Allocation and Graph K-Coloring

- K = number of available registers

- G = (V,E) where

- Vertex set V = {V<sub>s</sub> | s is a program variable}

- Edge  $V_{\rm s} V_{\rm t}$  in E if s and t can be live at the same time

- G is an 'interference graph'

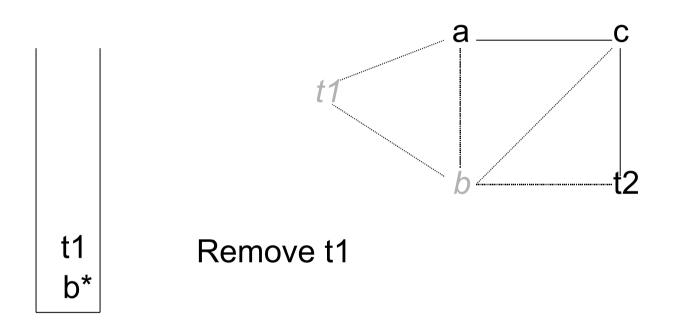

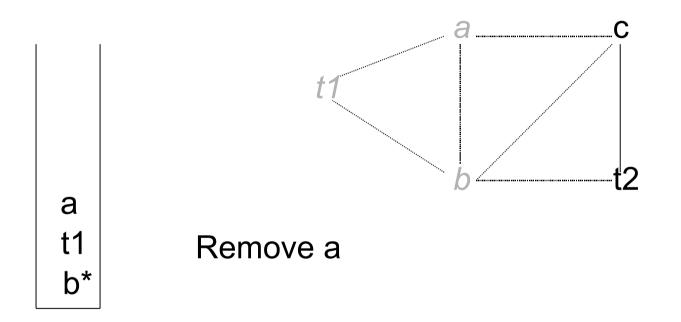

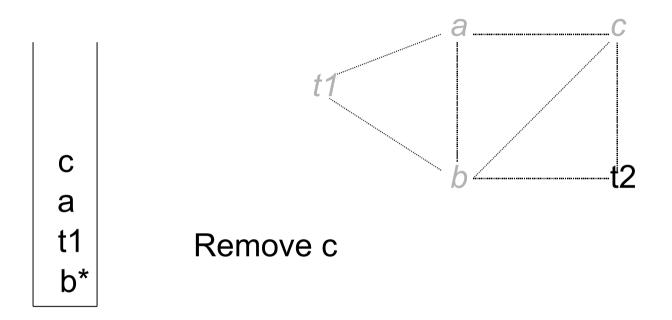

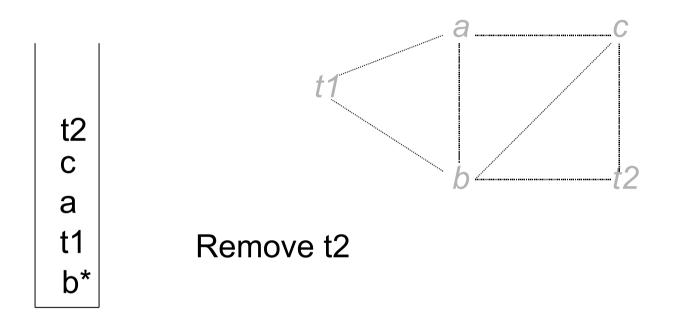

# Algorithm: K Registers

- Compute liveness information for the basic block. Assume, that every live variable will be stored in a register.

- Create interference graph G one node for each variable, an edge connecting any two variables alive simultaneously

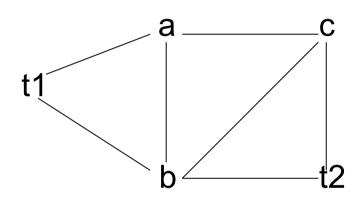

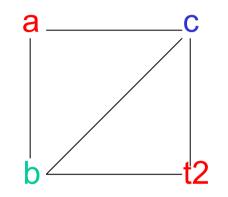

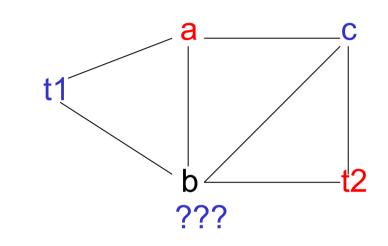

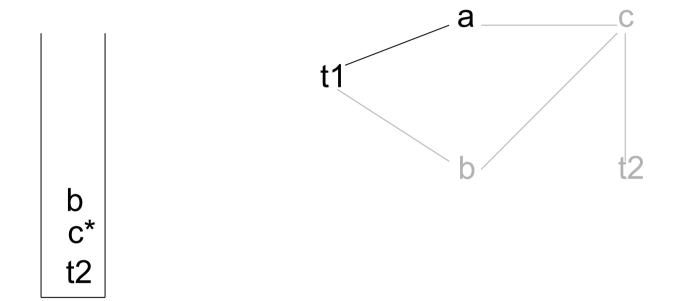

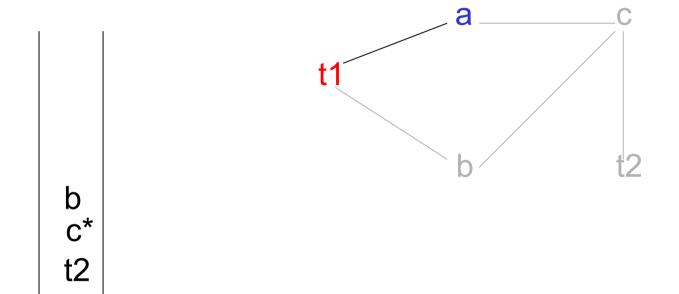

### **Example Interference Graph**

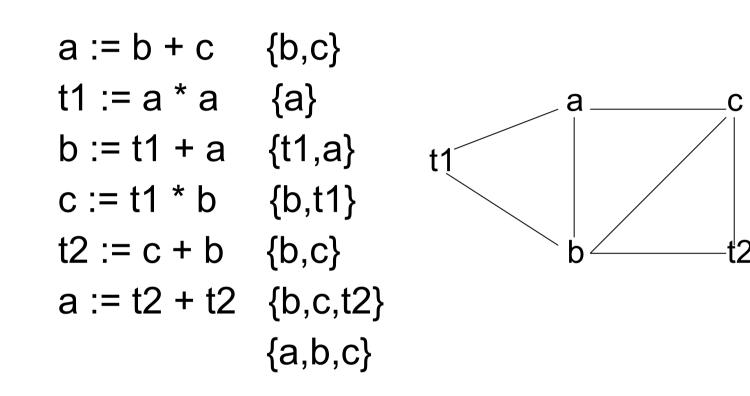

a := b + c{b,c}t1 := a \* a{a}b := t1 + a{t1,a}c := t1 \* b{b,t1}t2 := c + b{b,c}a := t2 + t2{b,c,t2}{a,b,c}

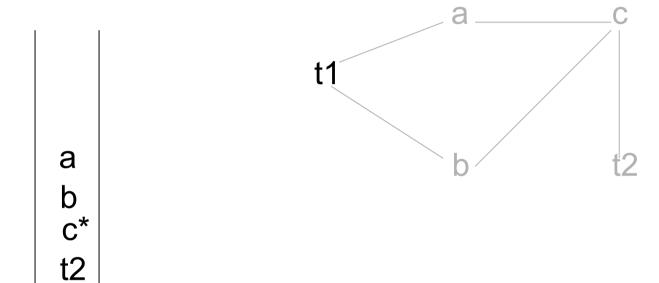

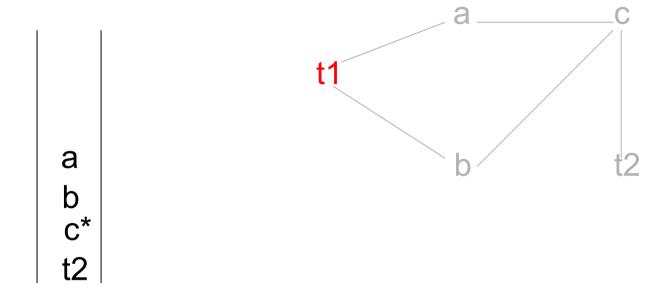

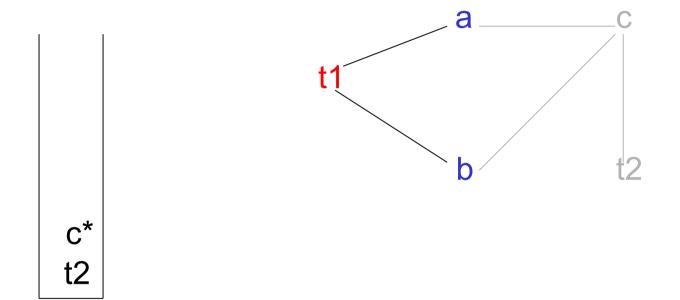

# Algorithm: K Registers

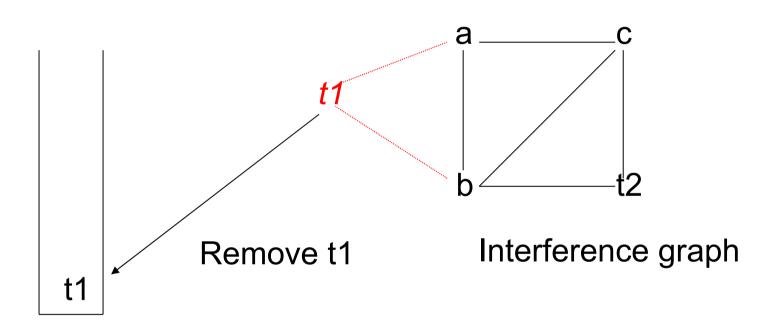

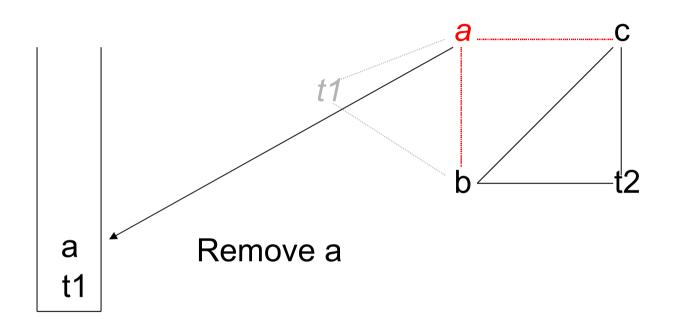

- 3. Simplify For any node m with fewer than K neighbors, remove it from the graph and push it onto a stack. If G m can be colored with K colors, so can G. If we reduce the entire graph, goto step 5.

- Spill If we get to the point where we are left with only nodes with degree >= K, mark some node for potential spilling. Remove and push onto stack. Back to step 3.

# Choosing a Spill Node

Potential criteria:

- Random

- Most neighbors

- Longest live range (in code)

- with or without taking the access pattern into consideration

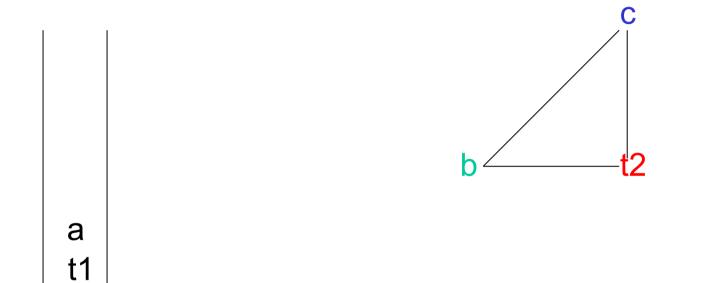

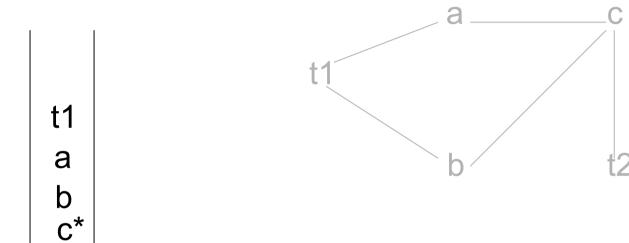

# Algorithm: K Registers

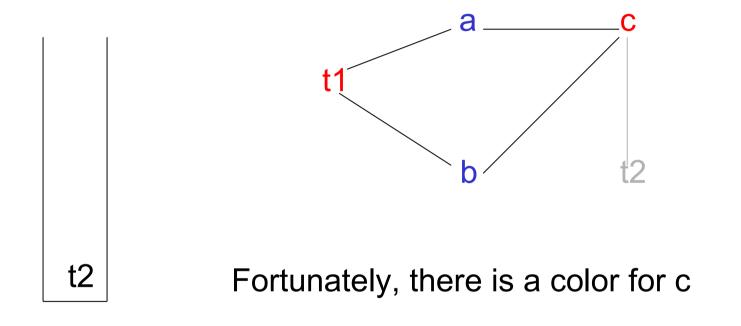

- 5. Assign colors Starting with empty graph, rebuild graph by popping elements off the stack, putting them back into the graph and assigning them colors different from neighbors. Potential spill nodes may or may not be colorable.

- Process may require iterations and rewriting of some of the code to create more temporaries

# Rewriting the Code

- Want to be able to remove some edges in the interference graph

- write variable to memory earlier

- compute/read in variable later

- Not all live variables will be stored in registers all the time.

#### Back to example

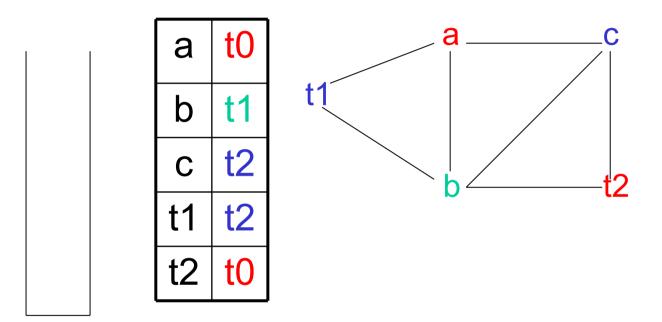

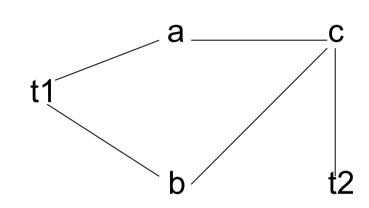

### Example, k = 3

## Rebuild the graph

Assume k = 3

c b a t1

t2

Assume k = 3

t1

## Back to example

- lw \$t1,b

- lw \$t2,c

- add \$t0,\$t1,\$t2

- mul \$t2,\$t0,\$t0

- add \$t1,\$t2,\$t0

- mul \$t2,\$t2,\$t1

- add \$t0,\$t2,\$t1

- add \$t0,\$t0,\$t0

- sw \$t0,a

- sw \$t1,b

- sw \$t2,c

#### Generated code: Basic

- lw \$t0,b

- lw \$t1,c

- add \$t0,\$t0,\$t1

- mul \$t1,\$t0,\$t0

- add \$t0,\$t1,\$t0

- mul \$t1,\$t1,\$t0

- add \$t2,\$t1,\$t0

- add \$t2,\$t2,\$t2

- sw \$t2,a

- sw \$t0,b

- sw \$t1,c

#### **Generated Code: Coloring**

- lw \$t1,b

- **lw** \$t2,c

- add \$t0,\$t1,\$t2

- mul \$t2,\$t0,\$t0

- add \$t1,\$t2,\$t0

- mul \$t2,\$t2,\$t1

- add \$t0,\$t2,\$t1

- add \$t0,\$t0,\$t0

- sw \$t0,a

- sw \$t1,b

- sw \$t2,c

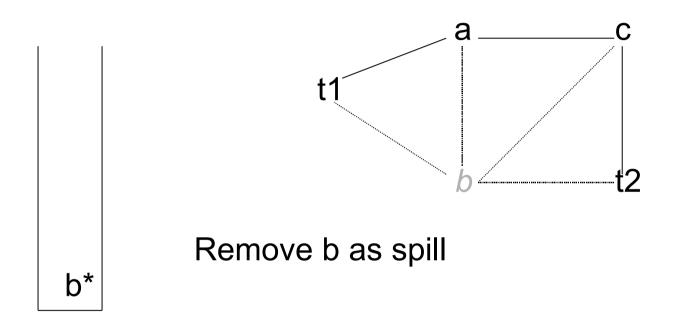

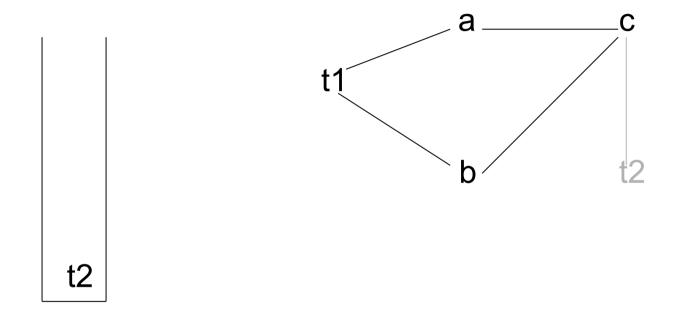

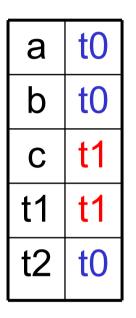

#### Example, k = 2

Assume k = 2

Can flush b out to memory, creating a smaller window

a := b + c {b,c} t1 := a \* a {a} b := t1 + a {t1,a} c := t1 \* b {b,t1} b to memory t2 := c + b {b,c} a := t2 + t2 {c,t2} {a,c}

t2

The graph is 2-colorable now

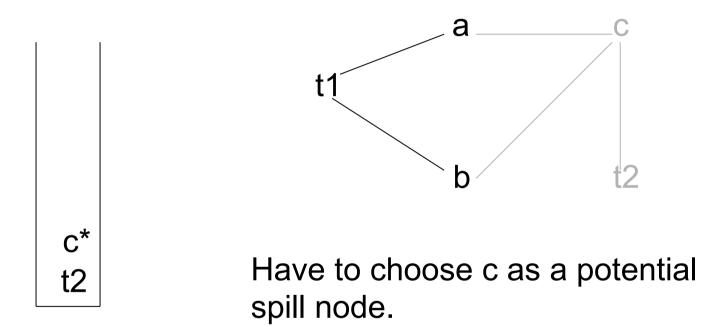

# The Code

| a := b - | + C |

|----------|-----|

|----------|-----|

- t1 := a \* a

- b := t1 + a

- c := t1 \* b

- b to memory

- t2 := c + b

- a := t2 + t2

| а  | tO |

|----|----|

| b  | t0 |

| С  | t1 |

| t1 | t1 |

| t2 | tO |

- lw \$t0,b

- lw \$t1,c

- add \$t0,\$t0,\$t1

- mul \$t1,\$t0,\$t0

- add \$t0,\$t1,\$t0

- mul \$t1,\$t1,\$t0

- sw \$t0,b

- add \$t0,\$t1,\$t0

- add \$t0,\$t0,\$t0

- sw \$t0,a

- sw \$t1,c