# Electronic Technology Design and Workshop

Presented and updated by

Przemek Sekalski DMCS room 2

2007

**Technical University of Lodz**

# Electronic Technology Design and Workshop

## Lecture 4 Introduction to Microelectronics

Technical University of Lodz

#### **ETDW course road map**

- ✓ Schematic edition, libraries of elements

- ✓ Circuit simulation & netlist generation

- ✓ Microelectronics full custom design and simulation

- ✓ Microelectronics simple layout synthesis

- ✓ Hardware description languages behavioural description

- ✓ Logic & sequential synthesis programmable logic devices

- ✓ PCB design auto-routing

- Project bringing the pieces together

3

#### What is Microelectronics ?

## **MICROELECTRONICS** [gr.], part of electronics considering behavior, constructions and fabrication technology of $\rightarrow$ integrated circuits

4

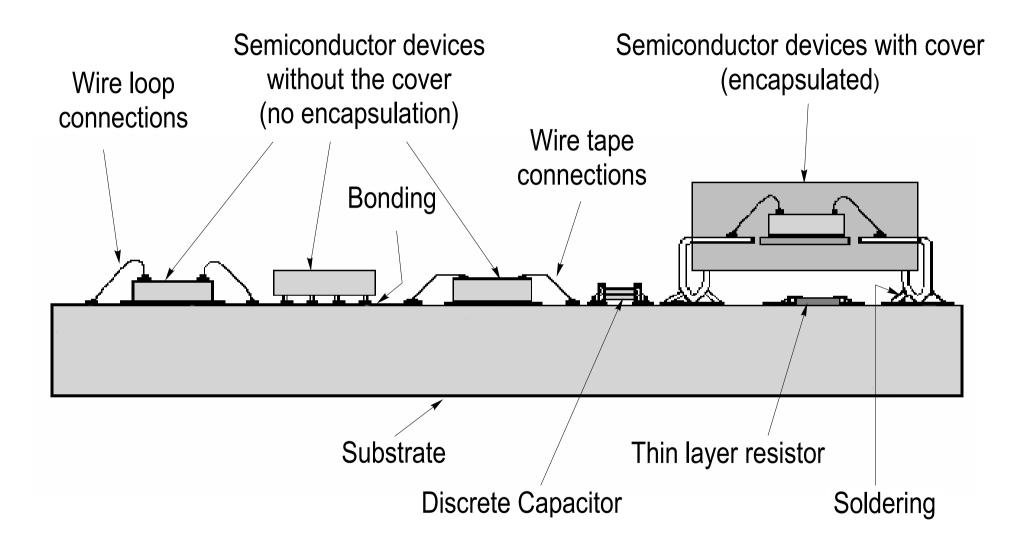

## INTEGRATED CIRCUIT, electronic device (microchip), where some or all components including interconnections are fabricated during single technological process in the single silicon substrate.

### **Integrated Circuit Types**

## • Hybrid

- Thick Layer

- Thin Layer

## • Monolithic

#### **Technical University of Lodz** Department of Microelectronics and Computer Sciences

7

#### **Thick Layer Integrated Circuits**

**Technical University of Lodz**

#### **Thick Layer Integrated Circuits**

#### Technical University of Lodz

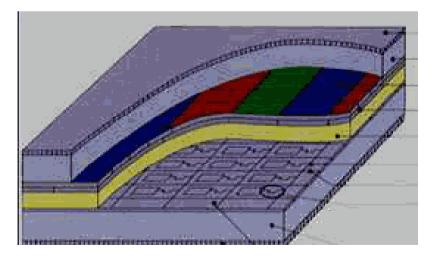

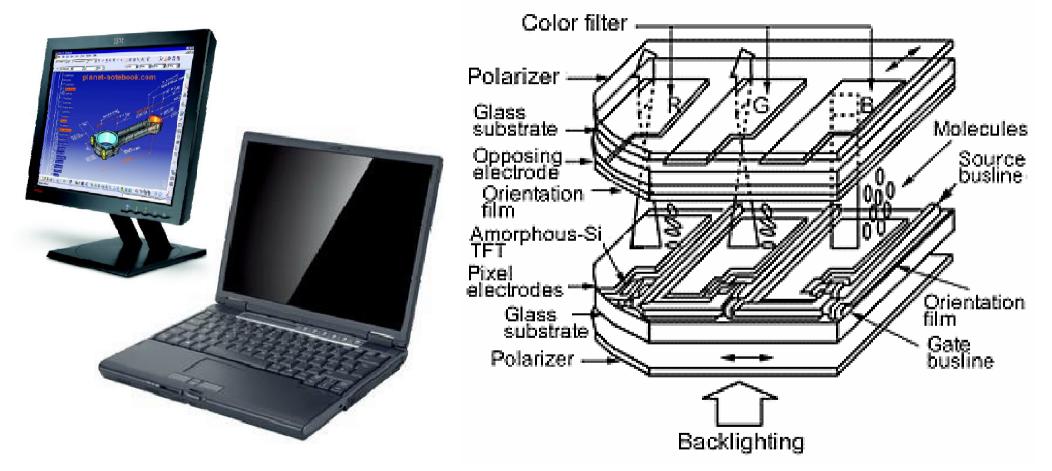

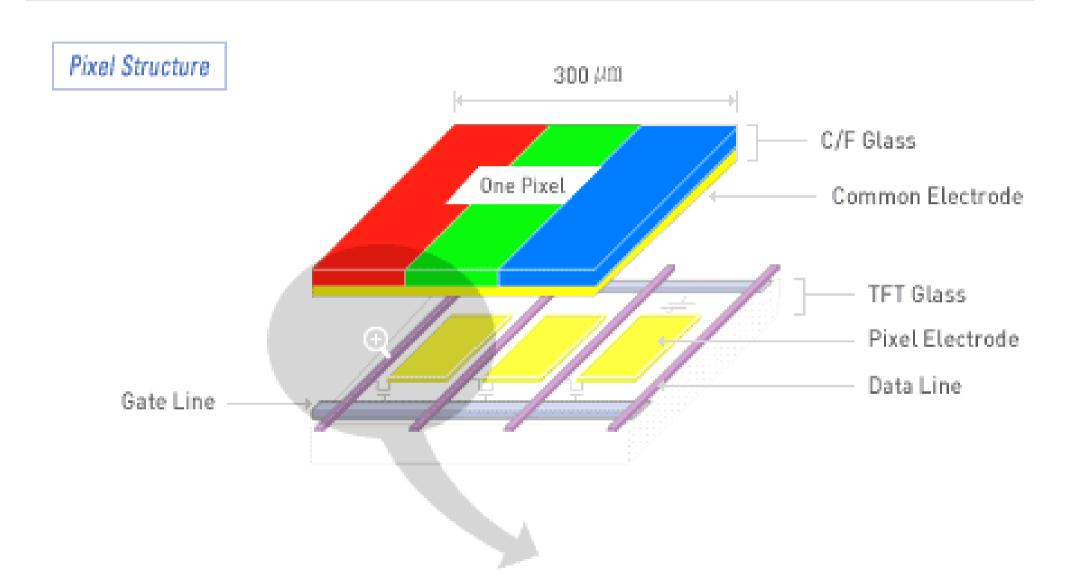

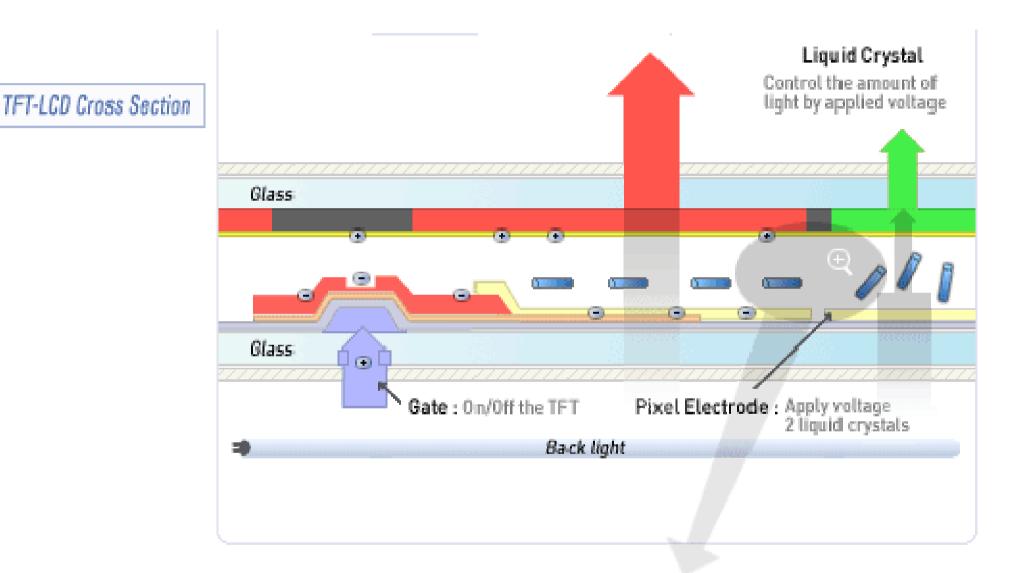

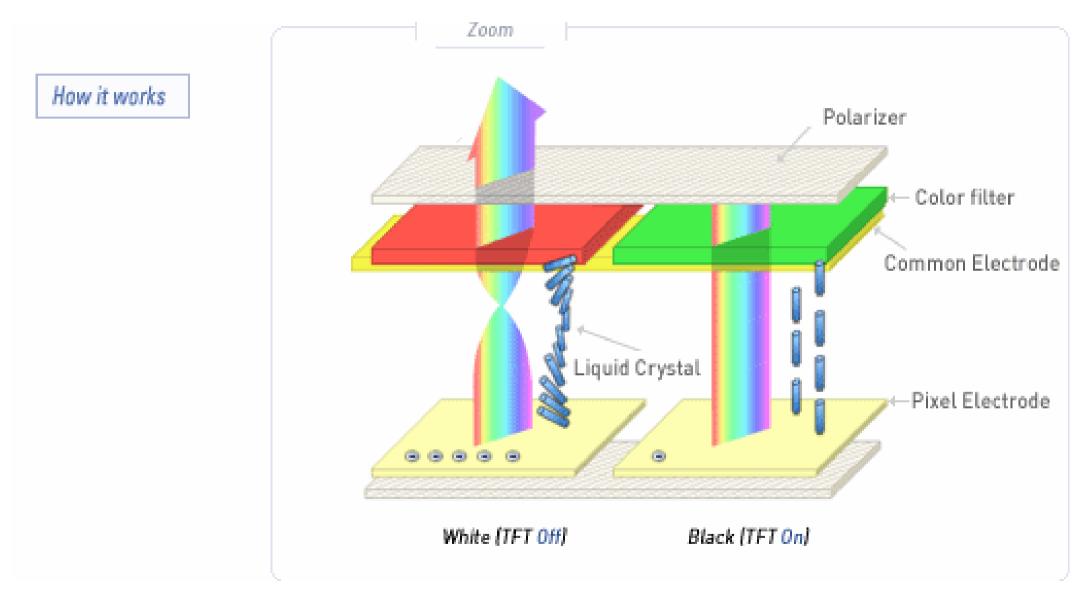

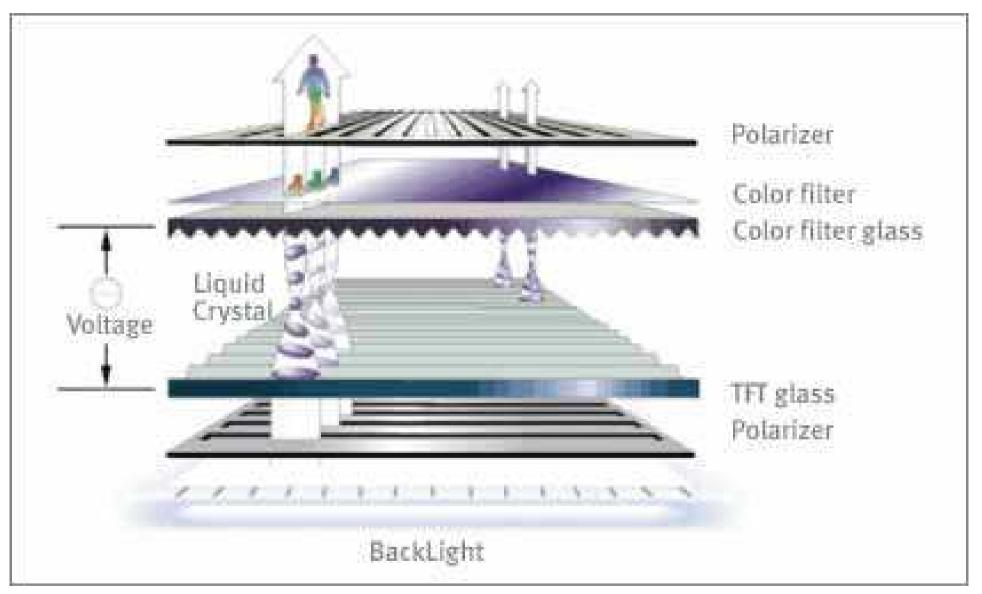

### **Thin Layer Integrated Circuits**

#### i.e. thin-film transistor (TFT)

10

## **TFT (1)**

#### Technical University of Lodz

**TFT (2)**

**Technical University of Lodz**

**TFT (3)**

**Technical University of Lodz**

**Department of Microelectronics and Computer Sciences**

12

**TFT (4)**

**Technical University of Lodz**

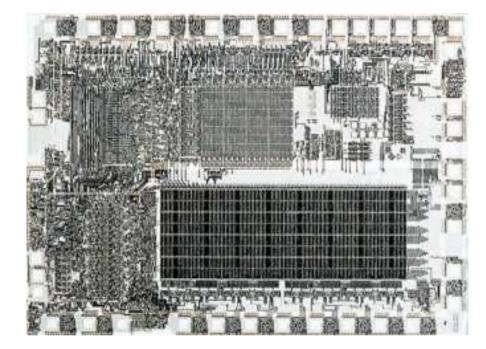

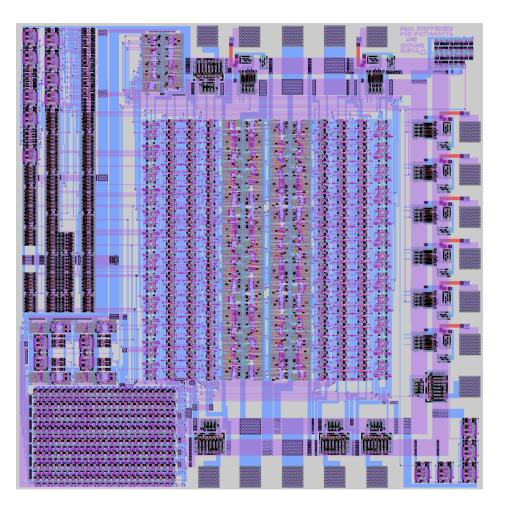

#### **Monolithic Integrated Circuits**

#### **Technical University of Lodz**

### **Integrated Circuits Advantages**

- Low cost

- Small dimensions

- Reliability

- Identity of temperature characteristics

### **Monolithic Integrated Circuits**

- Standard

- Application Specific (ASIC)

### **Standard Circuits Advantages**

- Low cost

- "off shelf" accessibility

- Verified reliability

- Many suppliers and manufacturers (usually)

### **Standard Circuits Disadvantages**

- Not optimized for specific problems

- Large area occupation

#### Technical University of Lodz

#### **ASIC Advantages**

- Easy parameter optimization for specific system

- Effective area usage

- Higher reliability and decreased number of devices on board

### **ASIC Disadvantages**

- High cost for low series

- High project costs

- Single Supplier

- Long designing time

### **Specialized Circuits**

- Programmable (FPLD)

- Semi-custom

- Custom

### **Field Programmable Logic Devices**

- Writable

- Writable / erasable

- Volatile

#### **"Field Engineer"**

#### **Technical University of Lodz**

#### **Semi-custom circuits**

- Gate array

- Linear array

#### **Technical University of Lodz**

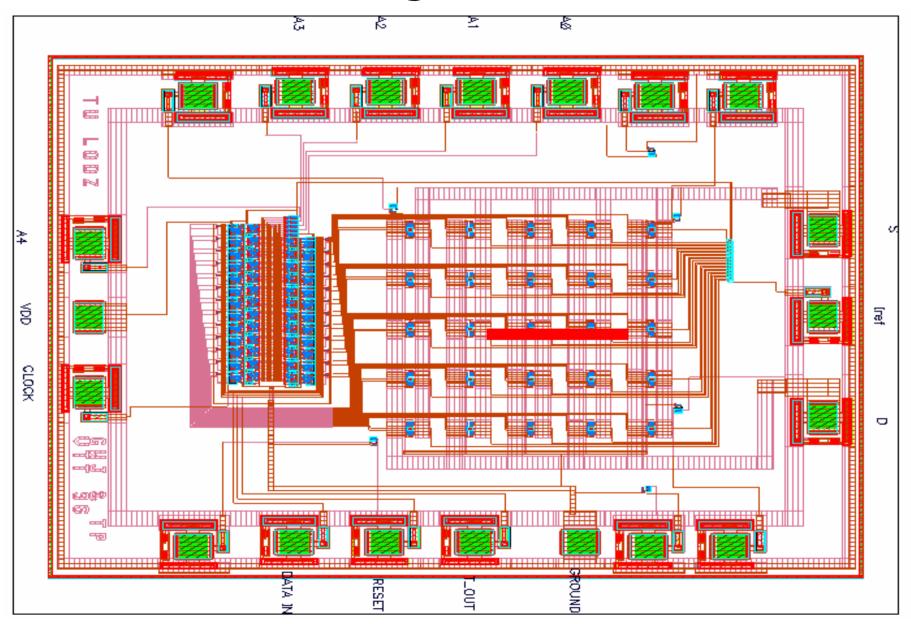

#### **Custom Circuits**

- Standard Cell

- Full Custom

### **Designer Tasks**

- Draw the circuit

- Draw the state diagram

- Describe behavior using high level language i.e. VHDL or Verilog

- Draw masks of integrated circuit

#### **Designer Task**

#### **Technical University of Lodz**

### **Design Tools**

- Xilinx

- Synopsis/Viewlogic

- Compass

- Cadence

- Mentor Graphics

28

### **Design tools functions**

- Edition of text, circuit scheme, topography

- Synthesis

- Topography and scheme comparison

- Design rules checking

- Component positioning and interconnecting

- Simulation

29

## MOS TRANSISTOR (Metal-Oxide-Semiconductor)

## BASICS

**Technical University of Lodz**

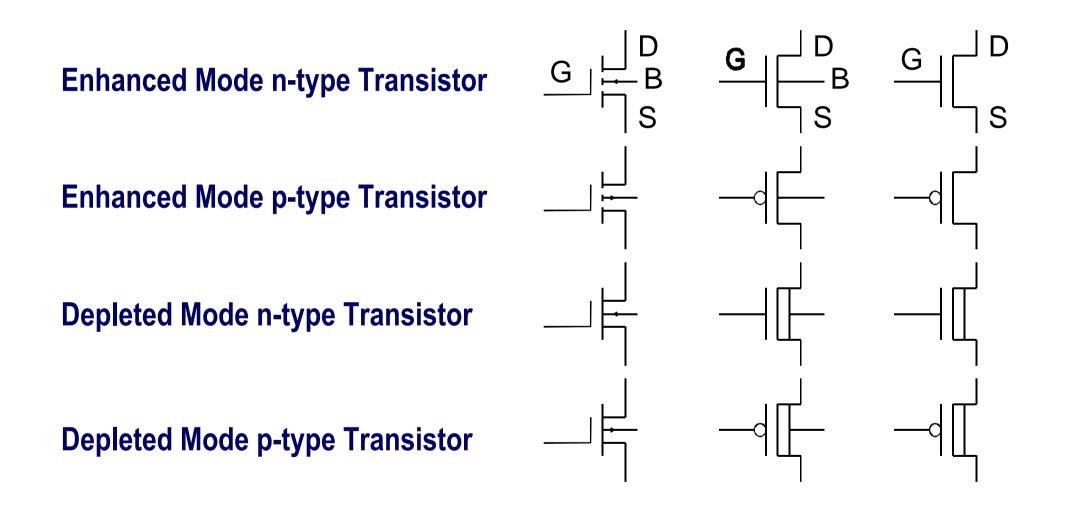

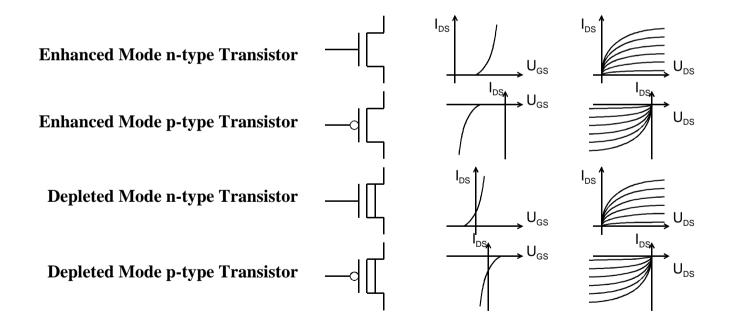

#### **MOS Transistor Symbols**

#### **MOS Transistor**

Technical University of Lodz

33

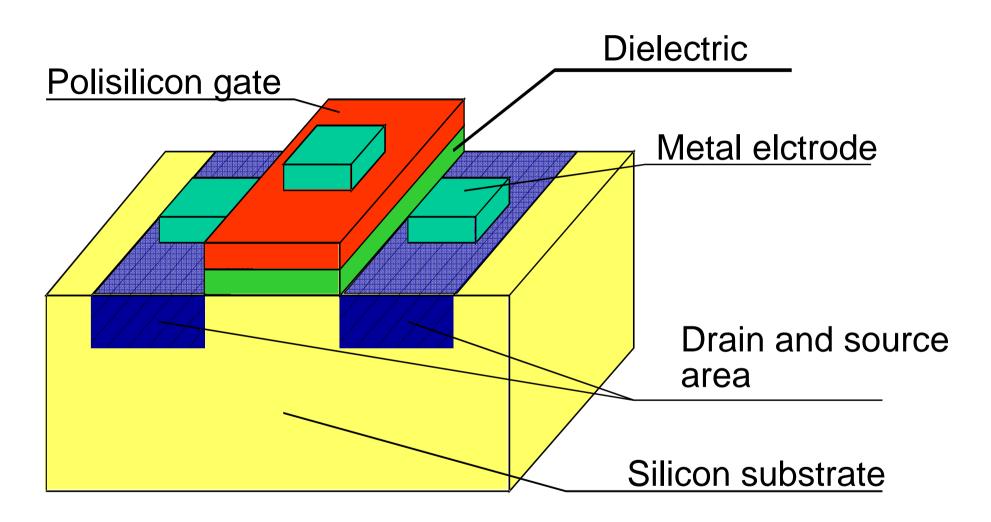

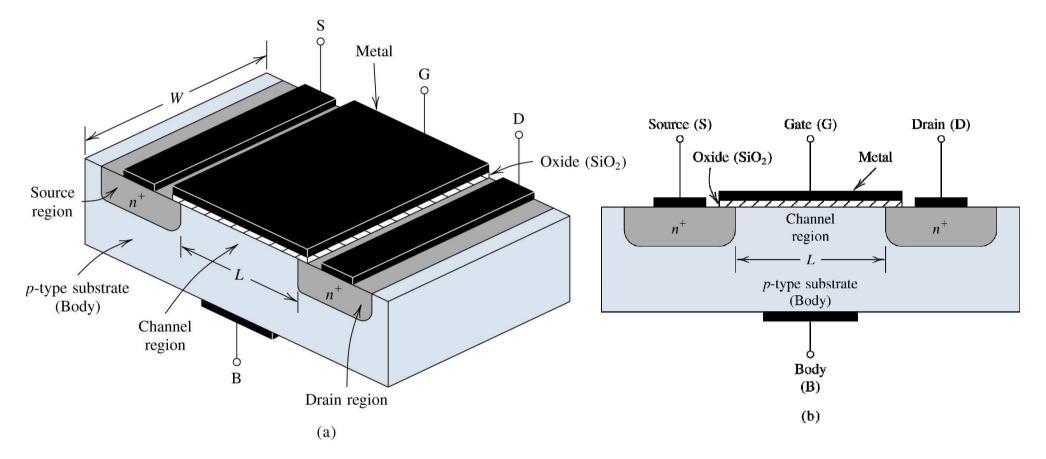

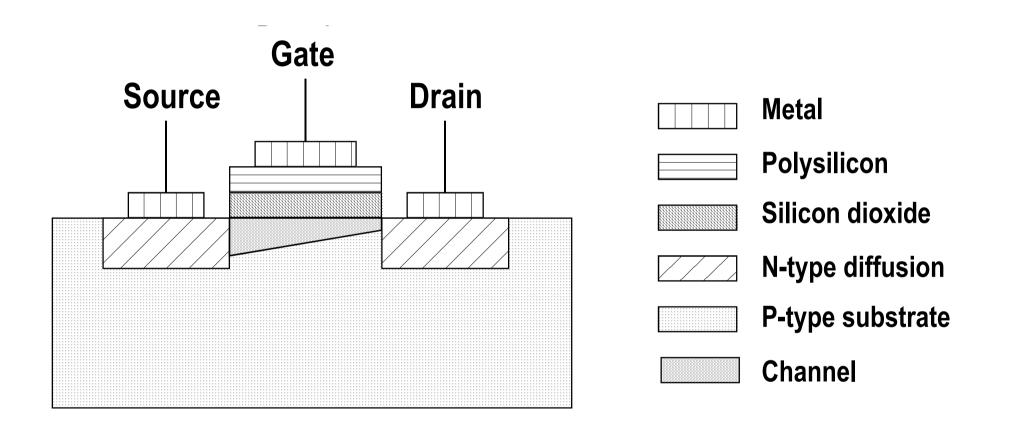

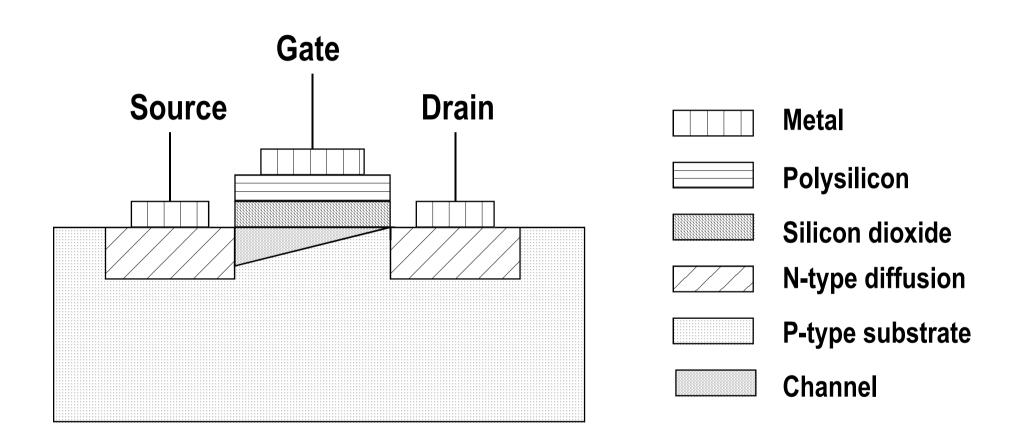

#### nMOS Transistor – physical structure

#### Enhancement-type NMOS transistor: (a) perspective view (b) cross section

#### Typically L = 1 to 10 $\mu$ m, W = 2 to 500 $\mu$ m, and the thickness of the oxide layer is in the range of 0.02 to 0.1 $\mu$ m.

Technical University of Lodz

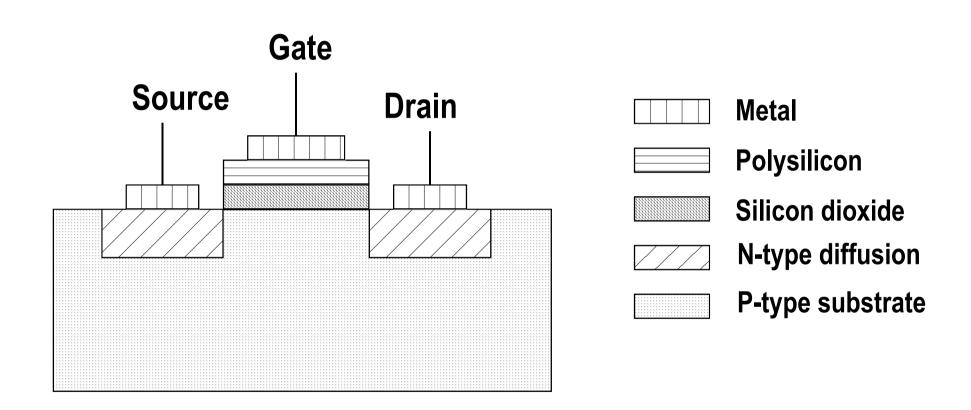

#### nMOS Transistor cross-section

**Technical University of Lodz**

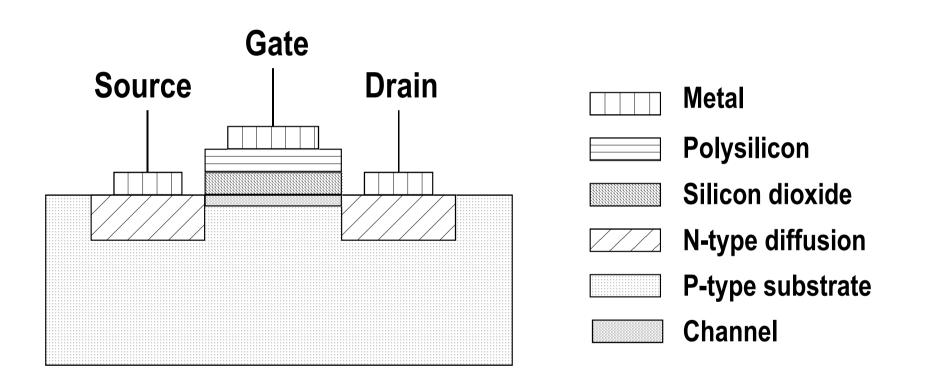

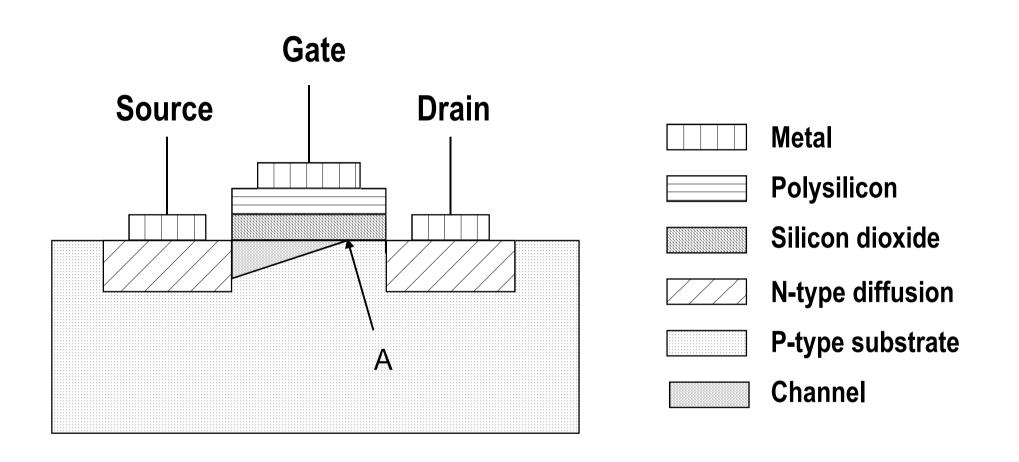

#### nMOS Transistor with polarised gate cross-section

#### **Technical University of Lodz**

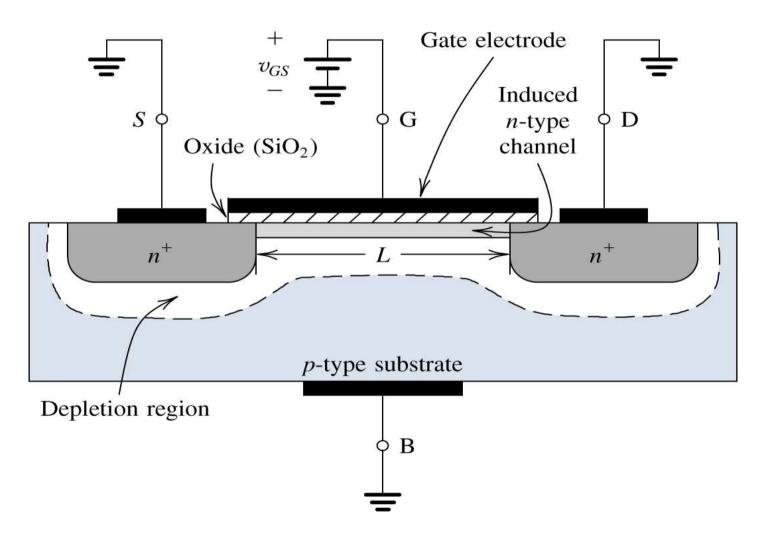

#### nMOS operation - positive voltage applied to the gate

#### An n channel is induced at the top of the substrate beneath the gate.

Technical University of Lodz

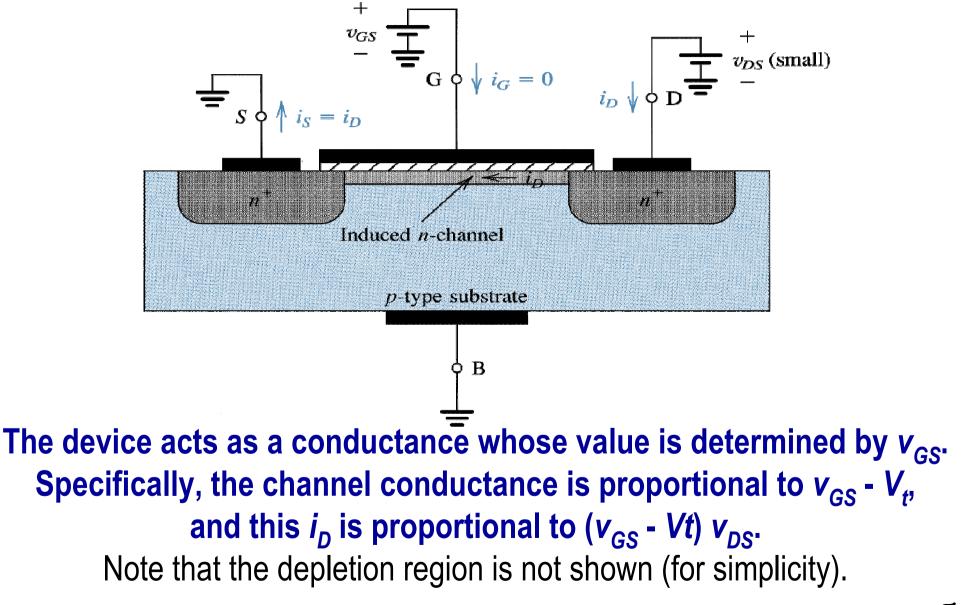

## nMOS operation - $V_{GS} > V_t$ and with a small $V_{DS}$ applied

Technical University of Lodz

Department of Microelectronics and Computer Sciences

#### **nMOS Transistor In Linear Range**

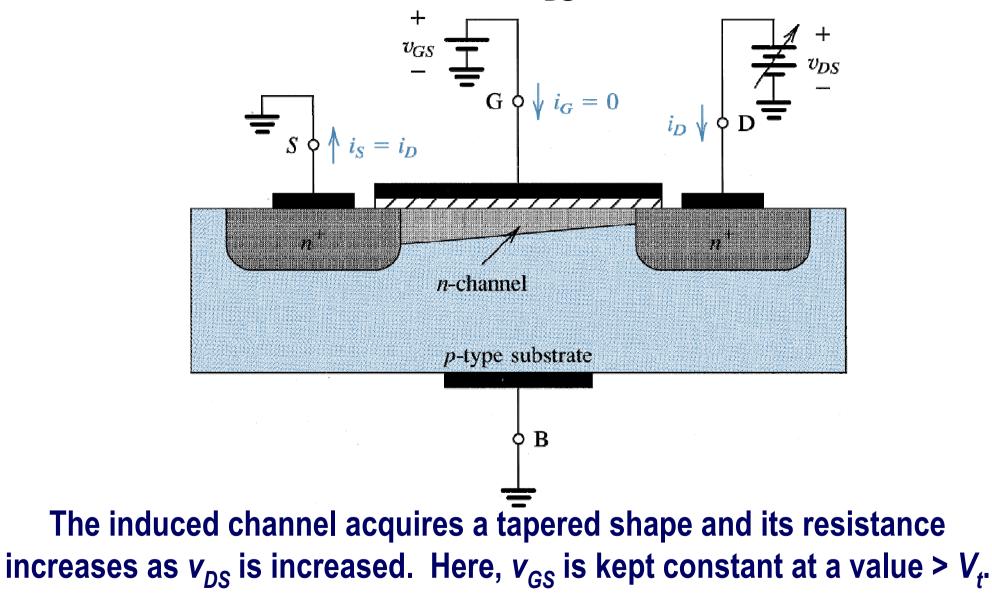

## nMOS operation - V<sub>DS</sub> is increased

Technical University of Lodz

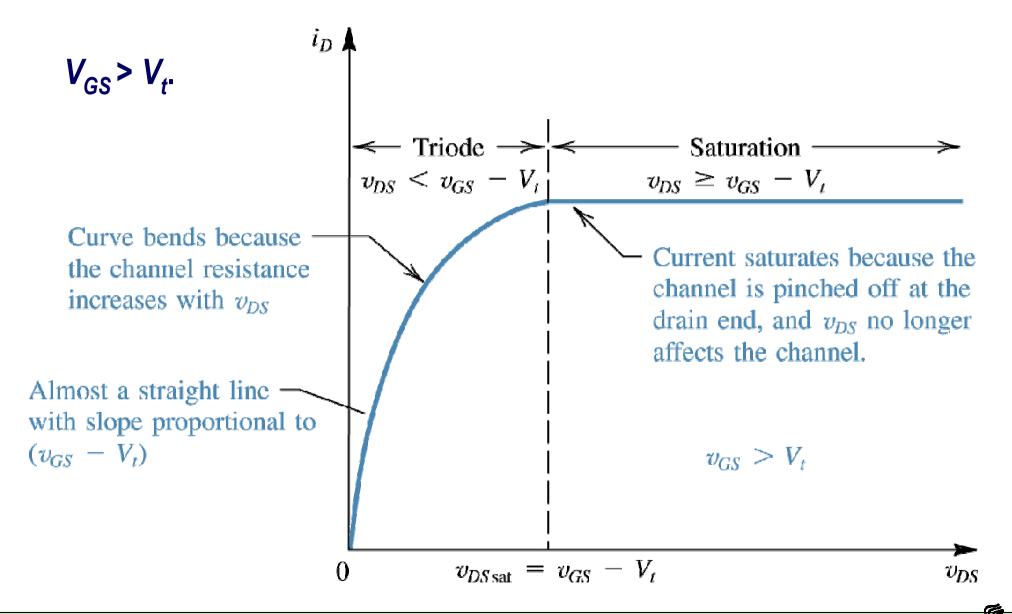

## The drain current versus the drain-to-source voltage V<sub>DS</sub>

Technical University of Lodz

## **nMOS Transistor Near The Saturation**

#### **Technical University of Lodz**

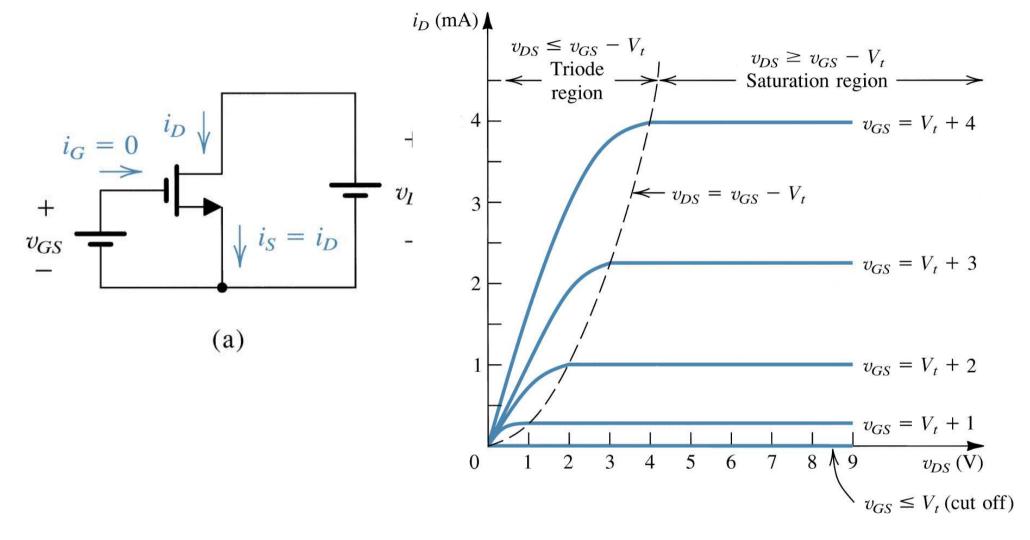

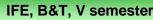

#### nMOS transistor operation – output characteristic

The output  $(i_D - v_{DS})$  characteristics for a device with  $V_t = 1$  V and  $k'_n(W/L) = 0.5$  mA/V<sup>2</sup>.

#### Technical University of Lodz

## **Saturated nMOS Transistor**

**Technical University of Lodz**

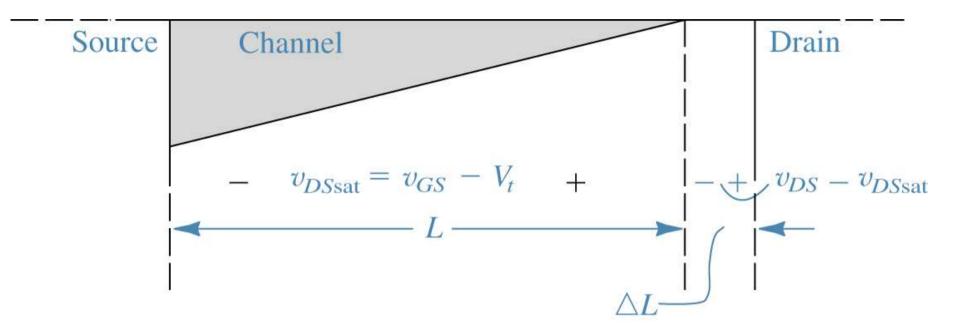

## **Saturated nMOS Transistor**

**Fig. 5.15** Increasing  $v_{DS}$  beyond  $v_{DSsat}$  causes the channel pinch-off point to move slightly away from the drain, thus reducing the effective channel length (by  $\Delta L$ ).

**Technical University of Lodz** Department of Microelectronics and Computer Sciences

**Fig. 5.11 (a)** An n-channel enhancement-type MOSFET with  $v_{GS}$  and  $v_{DS}$  applied and with the normal directions of current flow indicated. **(b)** The  $i_D - v_{DS}$ characteristics for a device with  $V_t$ = 1 V and  $k'_p(W/L) = 0.5 \text{ mA/V}^2$ .

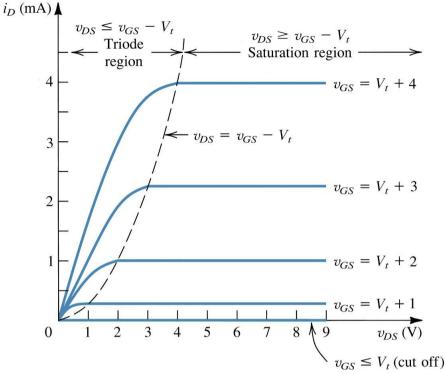

**Fig. 5.12** The  $i_D - v_{GS}$ characteristic for an enhancement-type NMOS transistor in saturation ( $V_t = 1 \text{ V}$ and  $k'_n(W/L) = 0.5 \text{ mA/V}^2$ ).

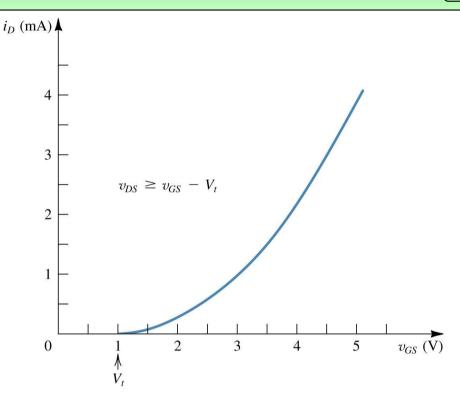

**Fig. 5.16** Effect of  $v_{DS}$  on  $i_D$  in the saturation region. The MOSFET parameter  $V_A$  is typically in the range of 30 to 200 V.

**Technical University of Lodz** Department of Microelectronics and Computer Sciences

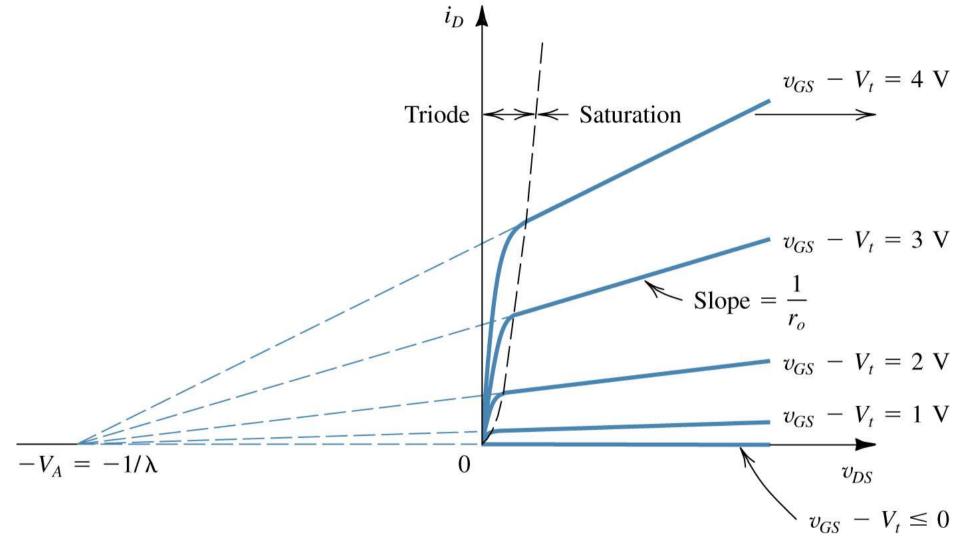

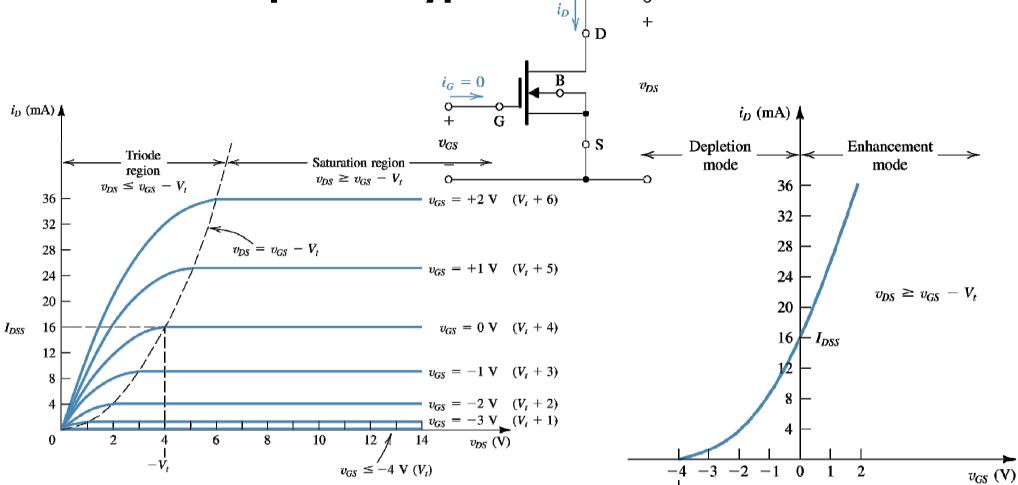

**Fig. 5.21** The current-voltage characteristics of a depletion-type *n*-channel MOSFET for which  $V_t = -4$  V and  $k'_n(W/L) = 2$  mA/V<sup>2</sup>: (a) transistor with current and voltage polarities indicated; (b) the  $i_D - v_{DS}$  characteristics; (c) the  $i_D - v_{GS}$  characteristic in saturation.

**Technical University of Lodz** Department of Microelectronics and Computer Sciences

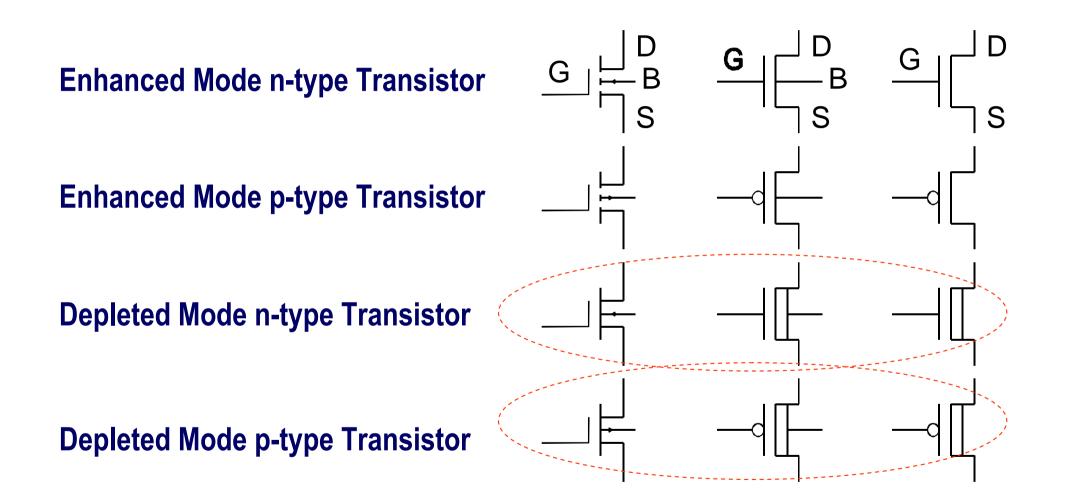

#### **MOS Transistor Symbols**

Technical University of Lodz

49

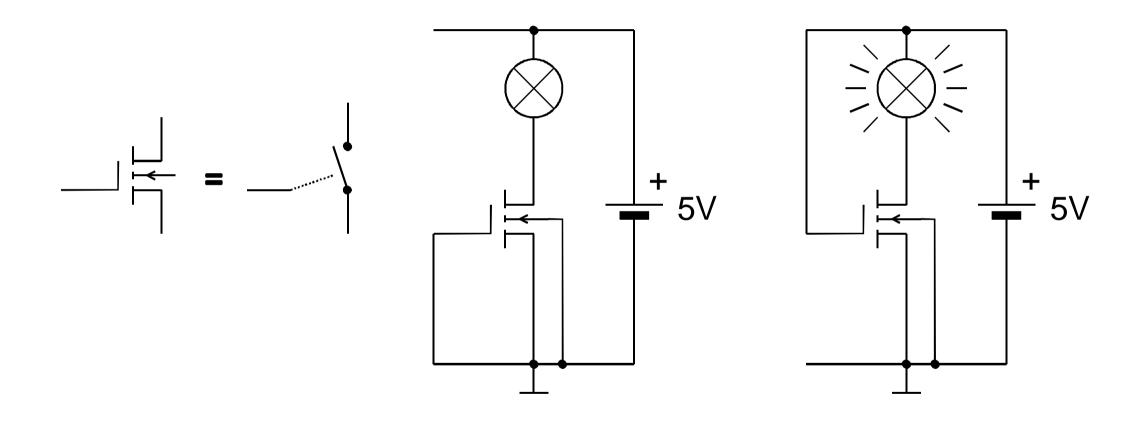

#### **nMOS Transistor As a Switch**

Technical University of Lodz

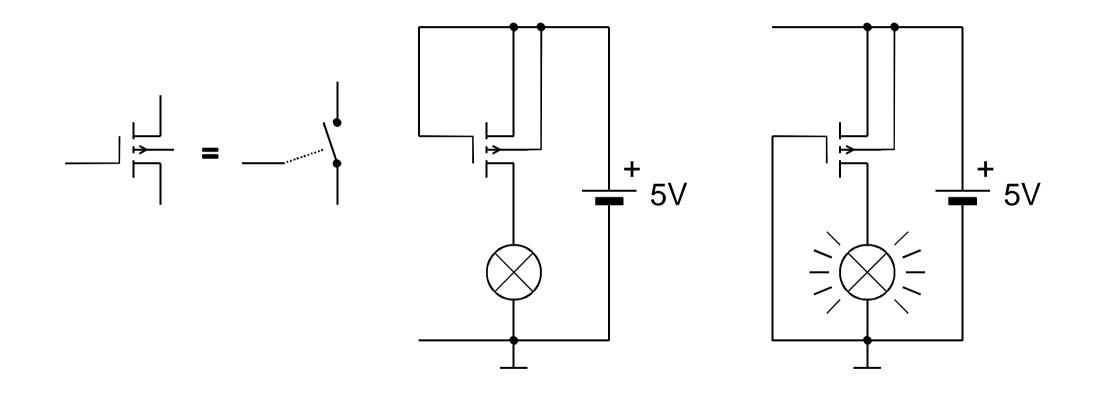

#### **pMOS Transistor As a Switch**

**Technical University of Lodz**

51

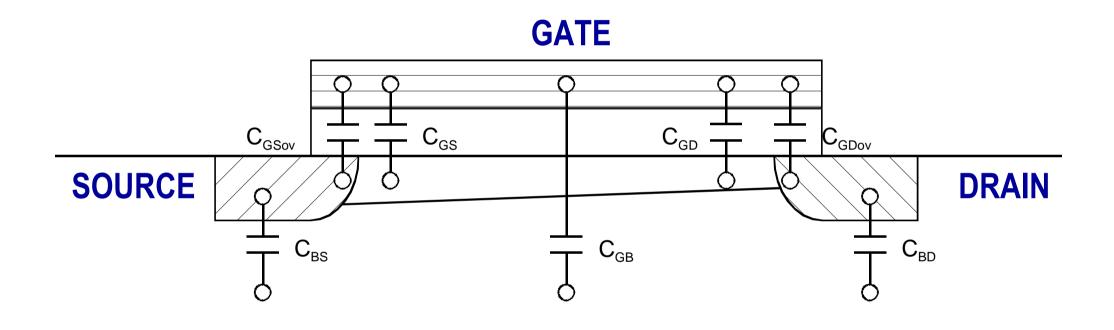

## **MOS Transistor Capacitances**

Technical University of Lodz

#### **MOS Transistor - summary**

| Zakres pracy                           | Napięcia na końcówkach                 |

|----------------------------------------|----------------------------------------|

| Zakres odcięcia, nieprzewodzenia       | $U_{GS} < U_{FB}$                      |

| Zakres liniowy, nienasycenia, triodowy | $U_{GS} \ge V_T i U_{DS} < U_{Dsat}$   |

| Zakres nasycenia, pentodowy            | $U_{GS} \ge V_T i U_{DS} \ge U_{Dsat}$ |

| Zakres podprogowy, słabej inwersji     | $U_{FB} \leq U_{GS} < V_T$             |

53

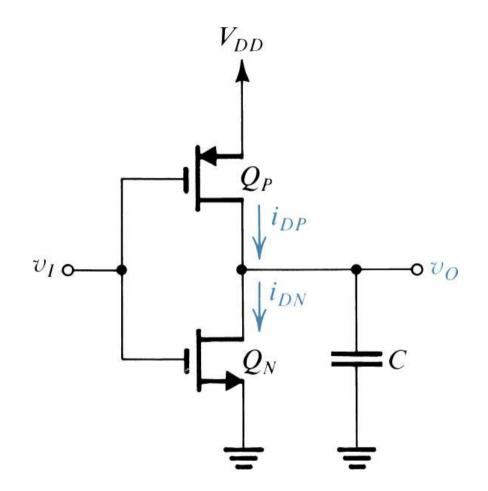

## **CMOS Inverter**

#### **Technical University of Lodz**

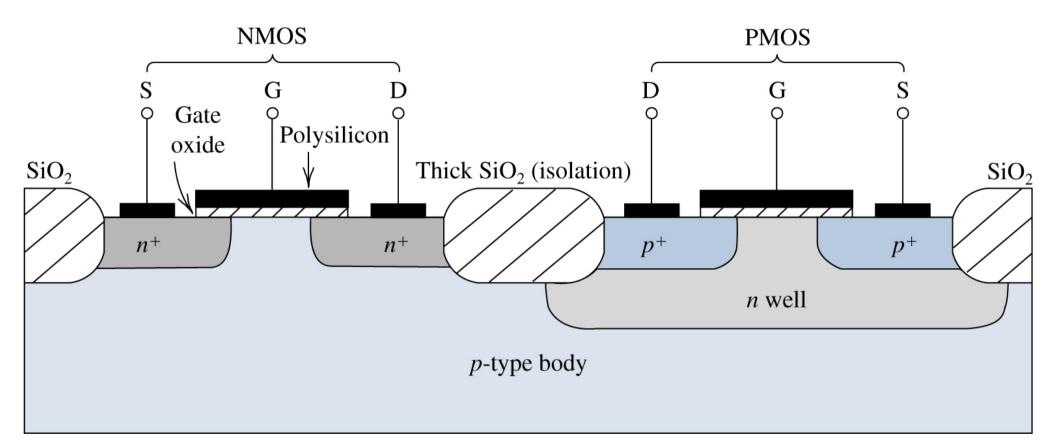

#### **CMOS inverter cross-section**

Note that the PMOS transistor is formed in a separate *n*-type region, known as an *n* well. Another arrangement is also possible in which an *n*-type body is used and the *n* device is formed in a *p* well.

**Technical University of Lodz** Department of Microelectronics and Computer Sciences

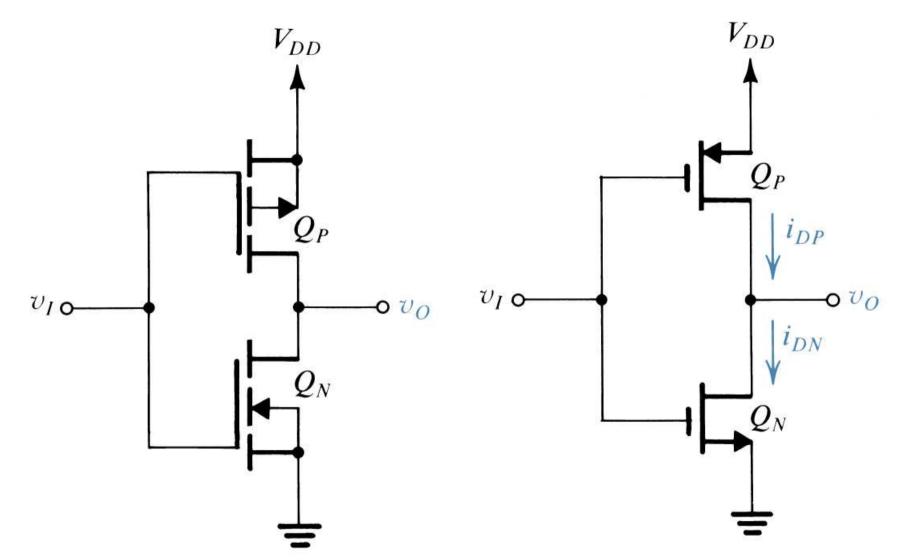

#### **CMOS** inverter scheme

#### **Technical University of Lodz**

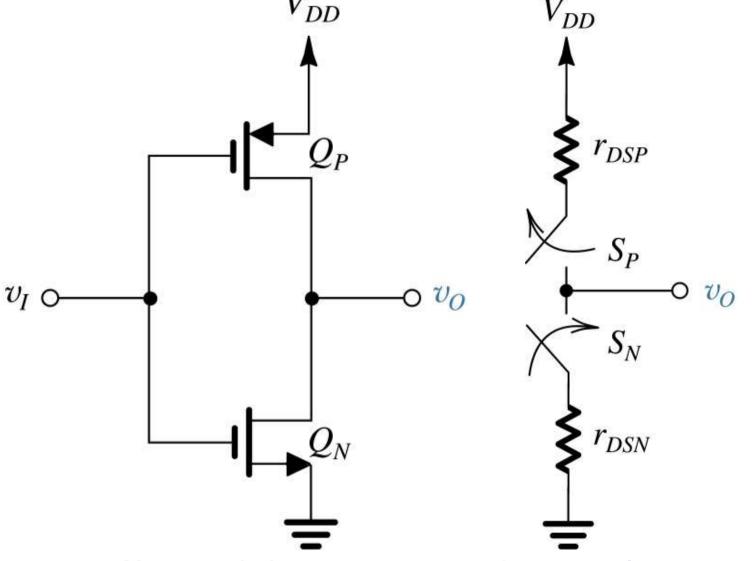

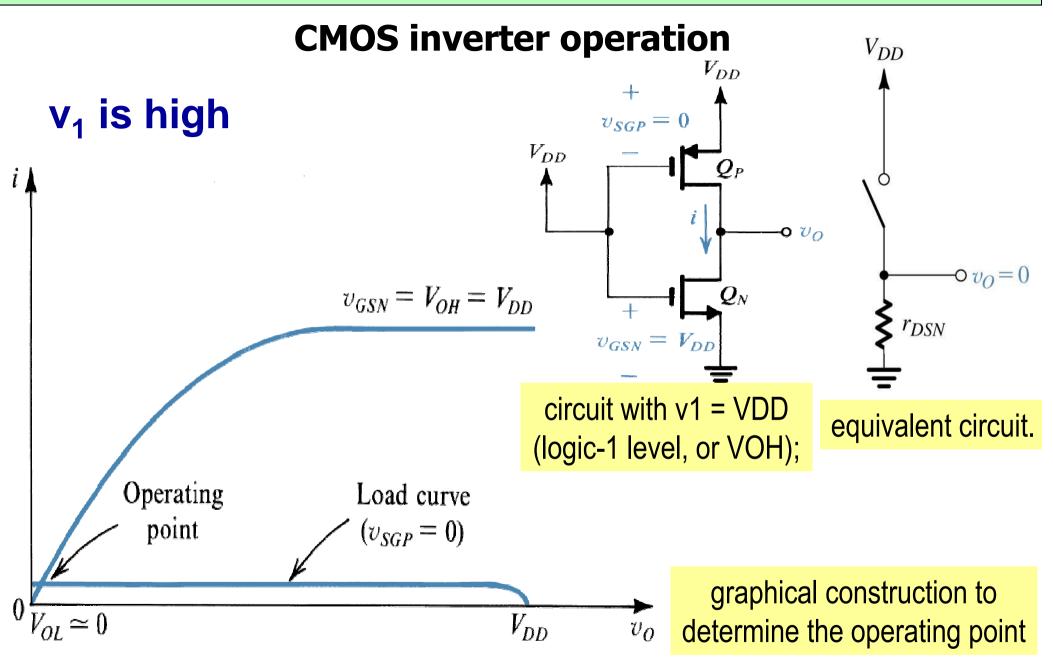

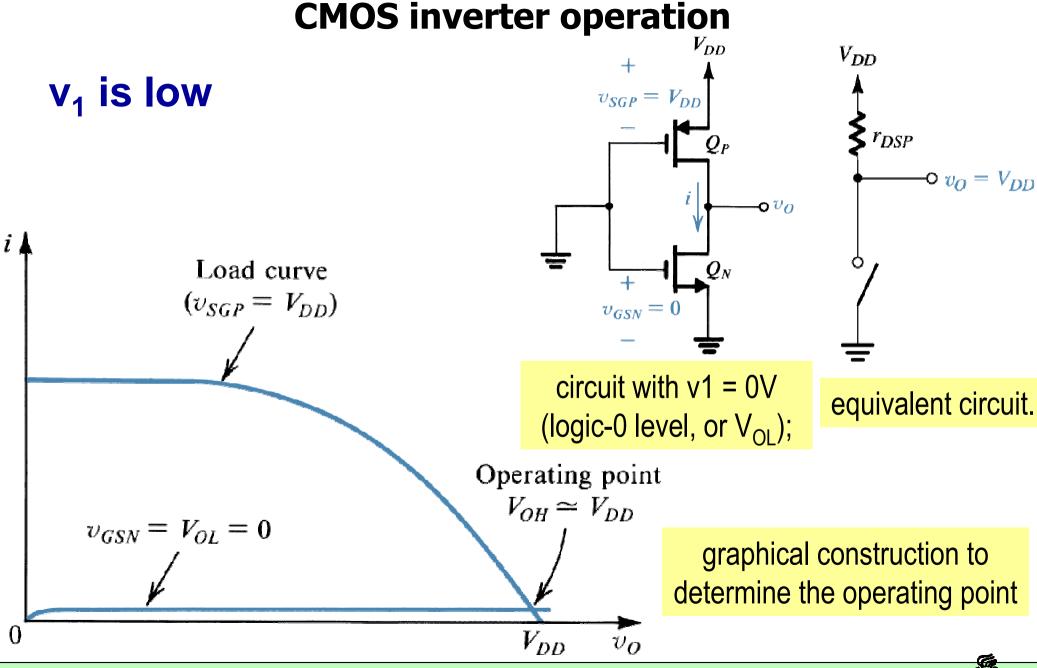

# **CMOS inverter and pair of switches** $V_{DD}$ $V_{DD}$

Note: switches must operate in a complementary fashion.

**Technical University of Lodz**

**Technical University of Lodz**

Technical University of Lodz

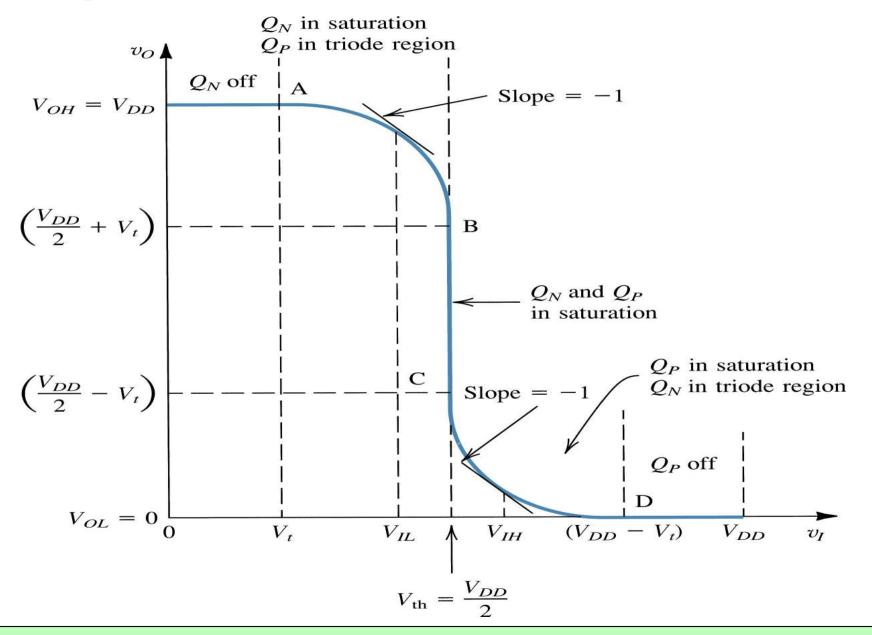

#### Voltage transfer characteristic of the CMOS inverter

#### **Technical University of Lodz**

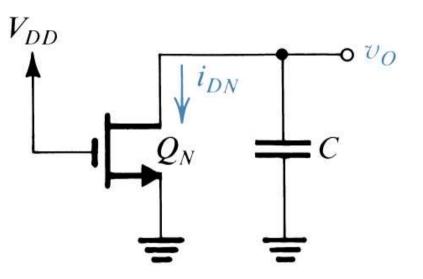

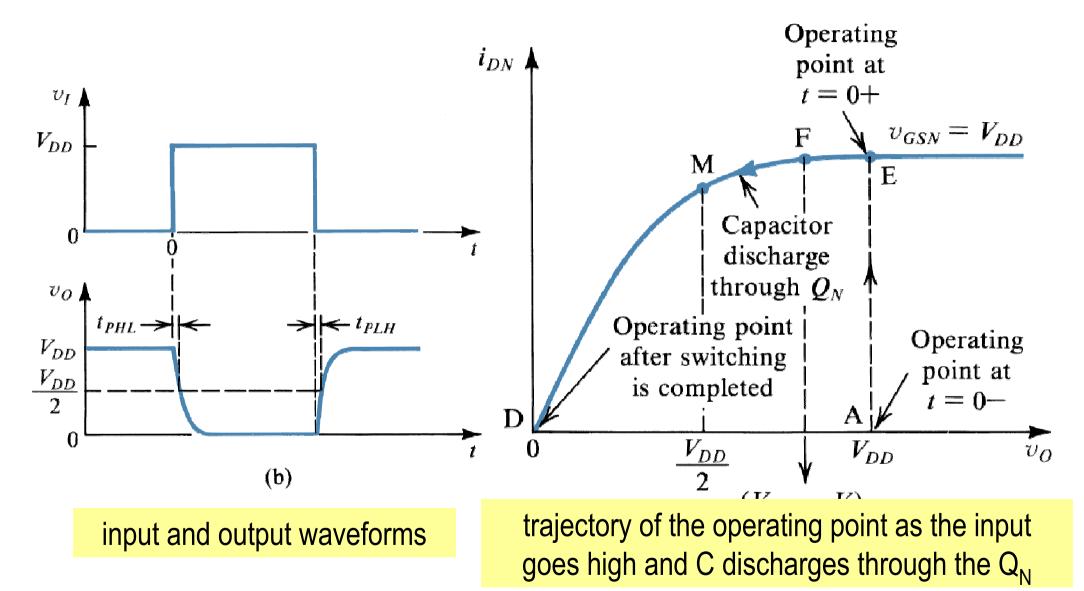

#### **Dynamic operation of a capacitive loaded CMOS inverter**

equivalent circuit during the capacitor discharge.

60

Technical University of Lodz

## Dynamic operation of a capacitive loaded CMOS inverter

**Technical University of Lodz**