# Electronic Technology Design and Workshop

Presented and updated by

Przemek Sekalski DMCS room 2

2007

**Technical University of Lodz**

# Electronic Technology Design and Workshop

# Lecture 6

# Microelectronics technology (part 2) Packages and Printed Circuits Boards

The lecture was prepared using wikipedia.org and other web pages dedicated to IC design

Technical University of Lodz

#### IFE, B&T, V semester

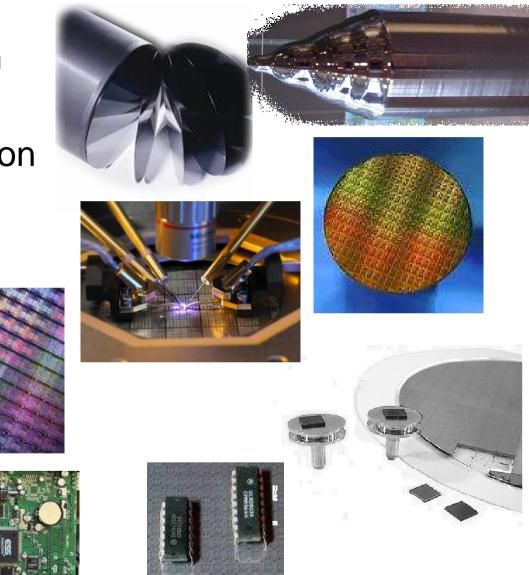

# **Silicon Integrated Circuits Technology**

- Silicon wafer fabrication

- Silicon devices fabrication

- On-wafer testing

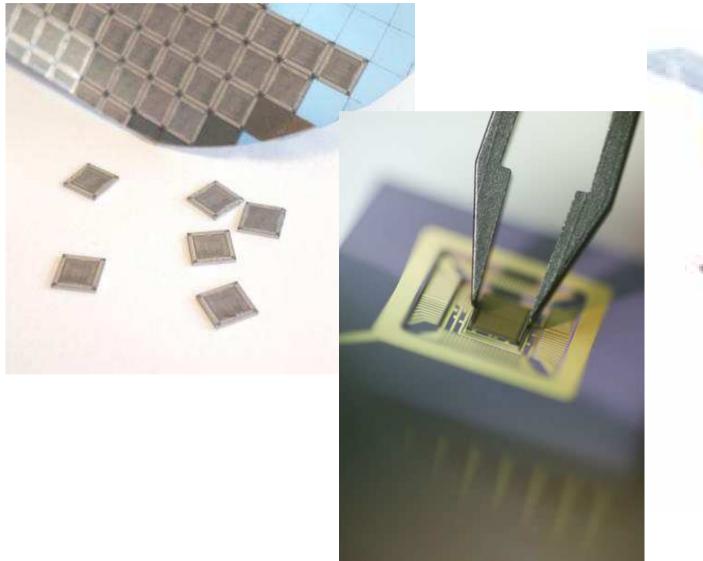

- Wafer-cutting

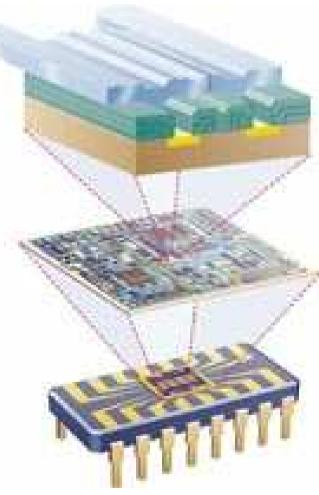

- Packaging

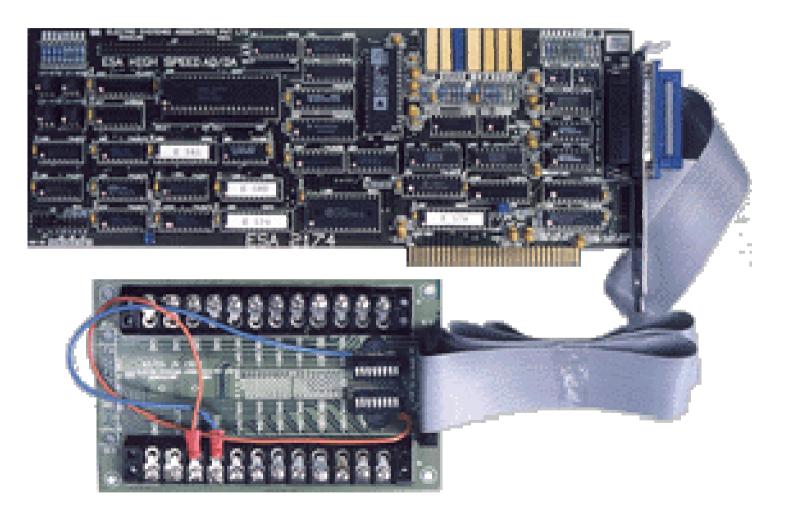

- PCB

**Technical University of Lodz** Department of Microelectronics and Computer Sciences

#### Introduction

#### **Technical University of Lodz**

#### **Printed Circuit Boards (PCBs)**

**Technical University of Lodz**

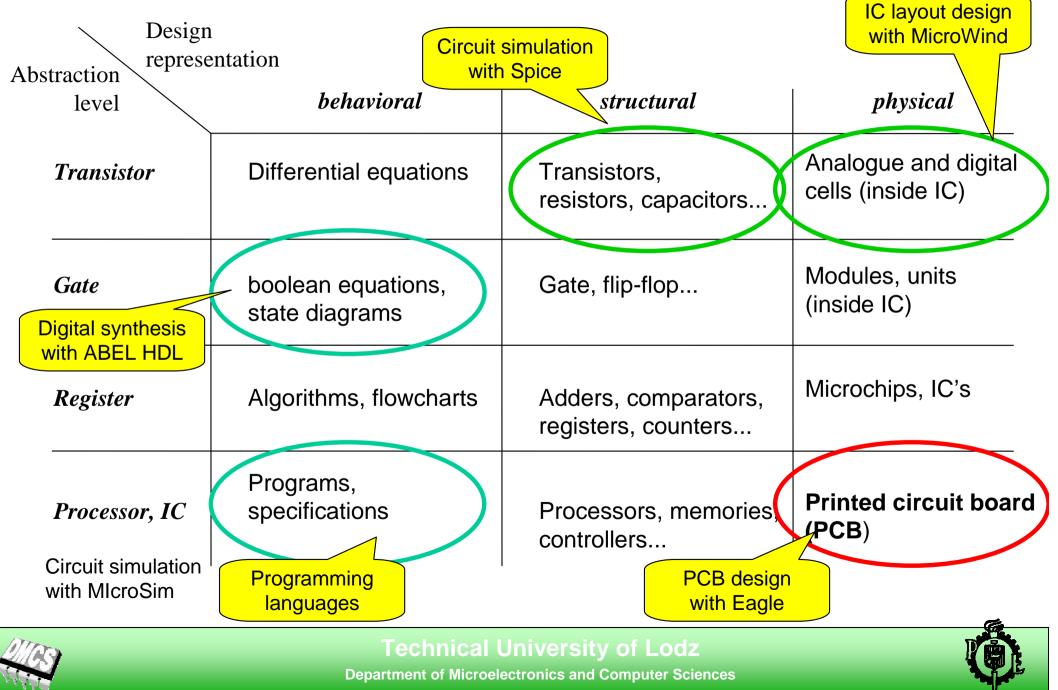

#### **Electronic levels of abstraction**

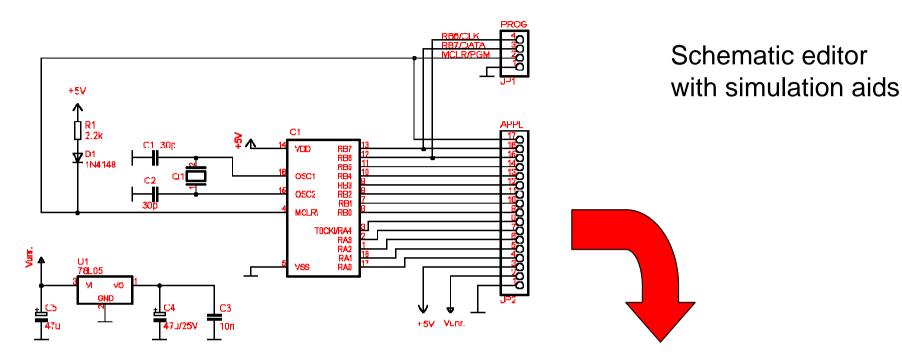

### **PCB Synthesis**

Automatic translation of the circuit description to less abstract representations, e.g.

- a) from behavioural to structural

- b) from structural to physical

- c) from behavioural to physical

| ysical     | behavioral | structural | physical |

|------------|------------|------------|----------|

| Transistor |            |            |          |

| Gate       |            |            |          |

| Register   |            |            |          |

| Processor  |            |            |          |

Not supported

(some support possible in specific cases - software-hardware codesign)

Partially supported (fully supported for certain types of digital designs)

Fully supported

7

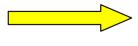

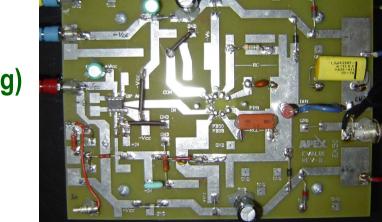

## **Types of PCBs**

- low maximal working temperature (125  $\degree$  250  $\degree$ )

- low thermal conductivity

**Technical University of Lodz**

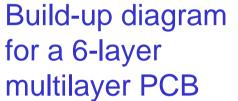

## **Types of PCBs**

Organic PCB

**Rigid** - epoxy glas laminate - most commonly used boards to host electronic components

Flexible - polyiamids films - used for flat or ribbon cables

Single sided - for simplest electronics and development boards

**Double sided -** for simple and medium complicated electronic circuits prototypes and development boards

Multilayer - for majority of high-level electronic circuits

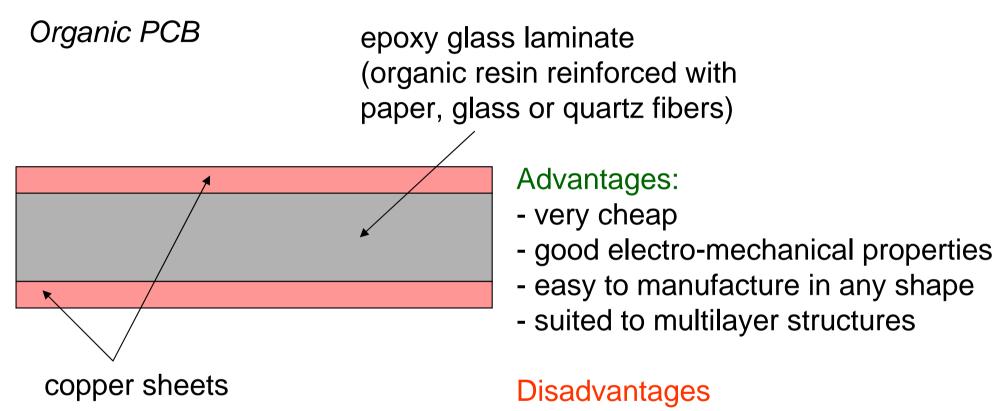

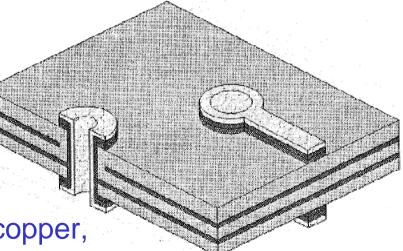

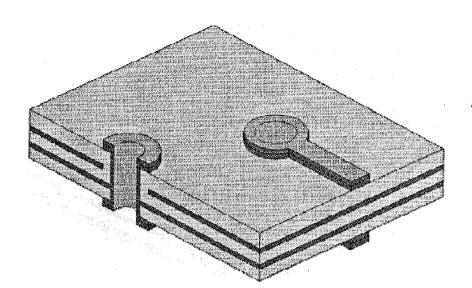

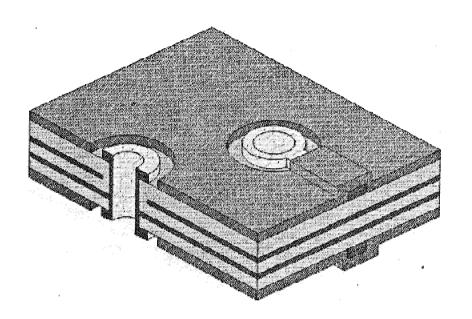

#### **Multilayer PCBs**

**Technical University of Lodz**

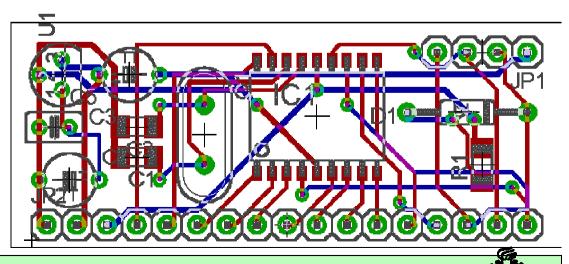

#### **Design of PCBs**

PCD editor with autorouting aids

#### **Technical University of Lodz**

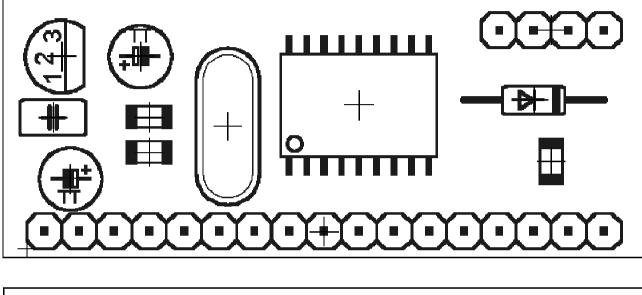

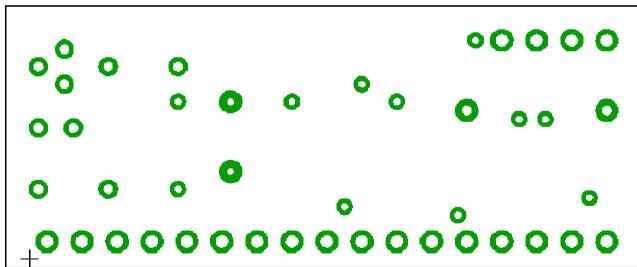

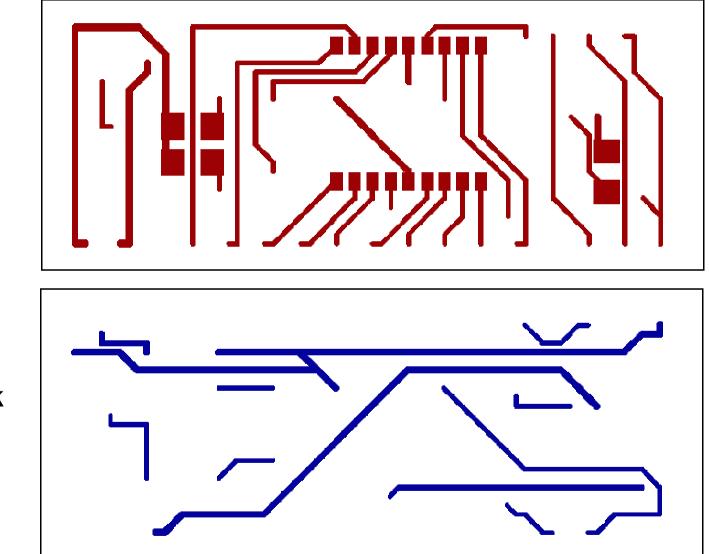

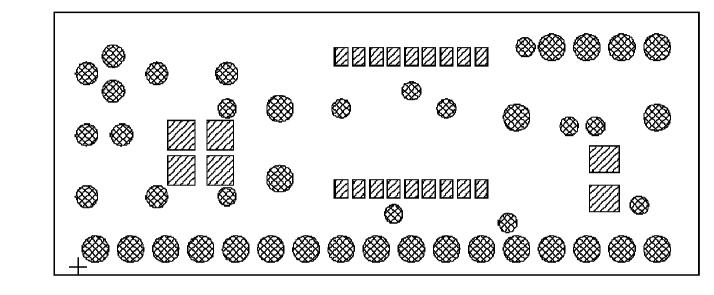

#### **Drawing PCB masks**

Positions of pads, holes and vias

**Technical University of Lodz**

#### **Drawing PCB masks**

**Top layer mask**

**Bottom layer mask**

**Technical University of Lodz**

#### **Drawing PCB masks**

**Solder mask**

**Technical University of Lodz**

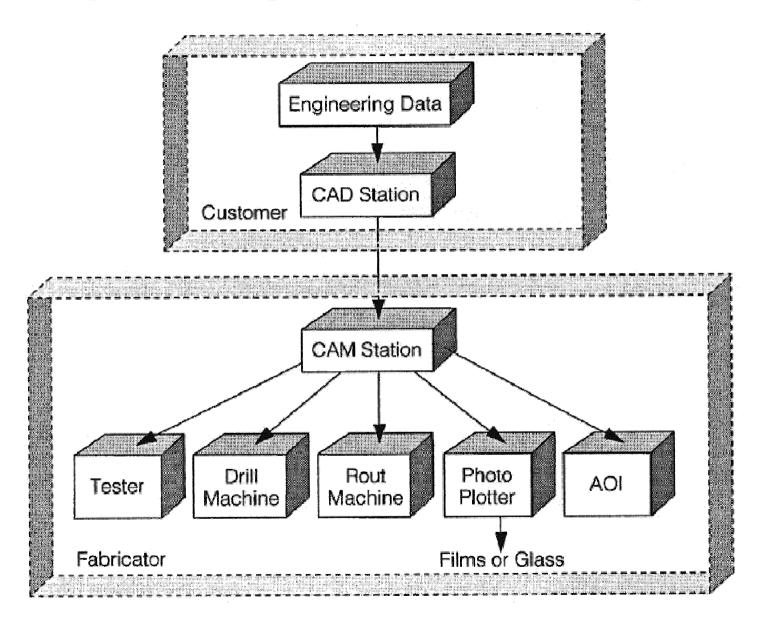

#### **Computer integrated manufacturing of PCB**

**Technical University of Lodz**

**Technical University of Lodz** Department of Microelectronics and Computer Sciences

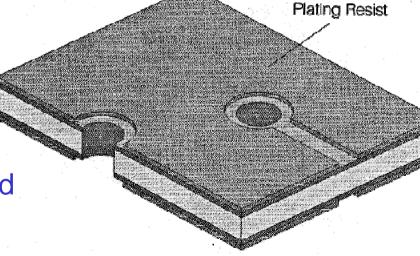

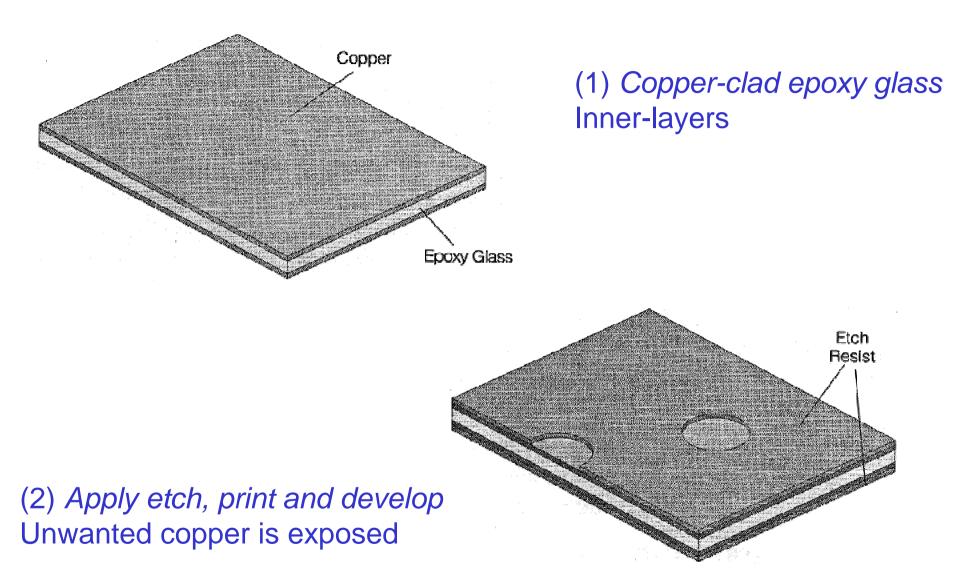

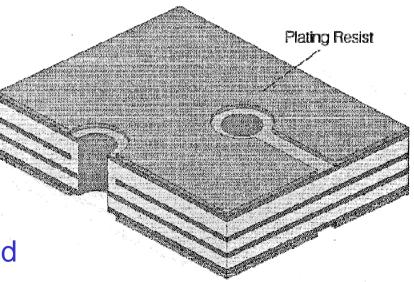

#### (4) Apply plating resist The desired circuitry is left uncovered

**Technical University of Lodz**

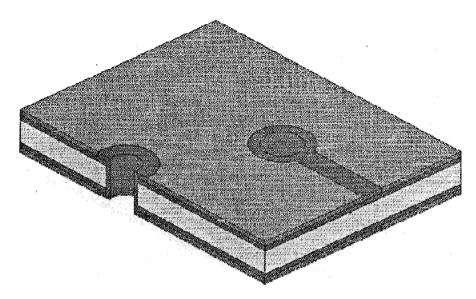

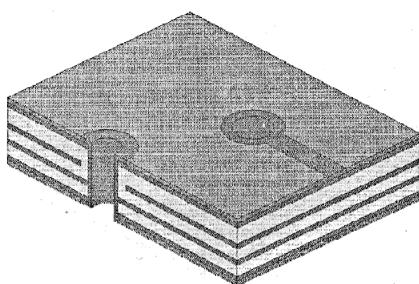

#### (5) Electroplate copper The specified thickness is electrolytically deposited (usually 0.001")

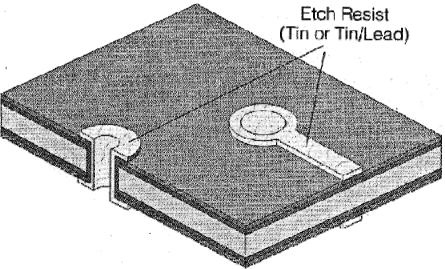

(6) Electroplate etch resist Tin or tin/lead is electrolytically deposited over the copper plating

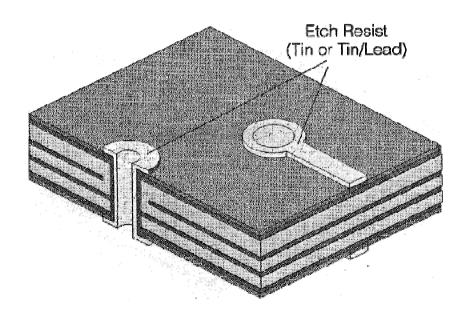

(7) Strip plating resist Plating resist is chemically removed, revealing the surface copper

#### (8) Etch

The unwanted copper is removed chemically by an etchant that attacks copper, but not tin or tin/lead

Technical University of Lodz

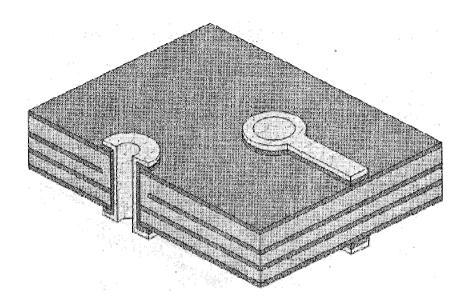

(9) Strip etch resist The tin or tin/lead is chemically removed

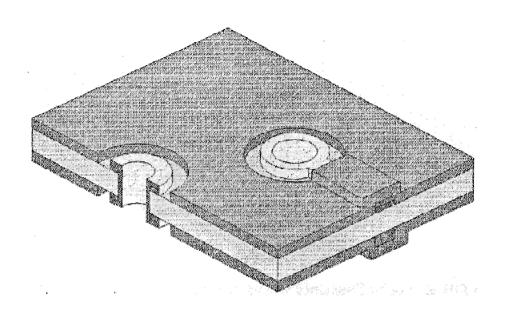

(10) Apply solder resist

The specified resist (dry film, liquid photoimageable or screen printed)

is applied to the surfaces of the PCB or panel

Solder Resist (Solder Mask)

**Technical University of Lodz**

(11) Solder coat Solder (tin/lead) is applied to the exposed copper and the excess solder is removed

#### **Technical University of Lodz**

#### **Technical University of Lodz**

Ö

Technical University of Lodz

**Technical University of Lodz**

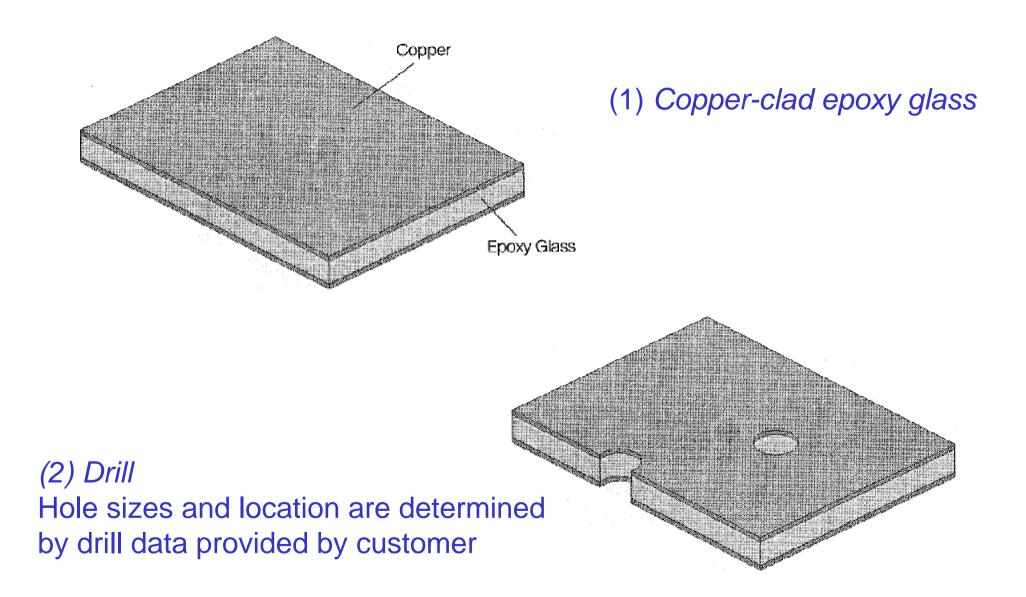

by drill data provided by customer

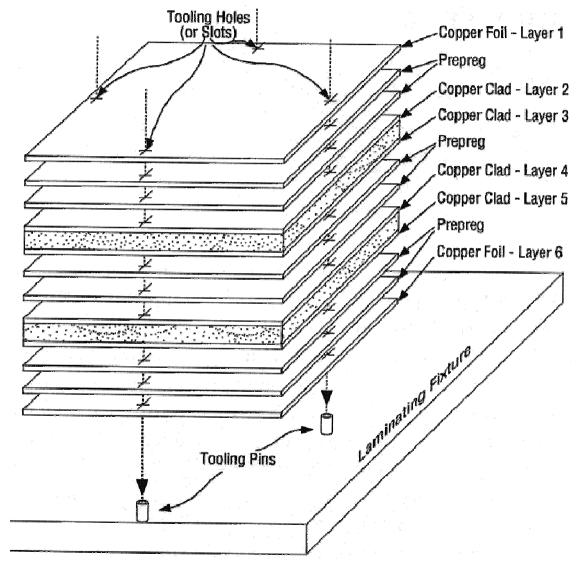

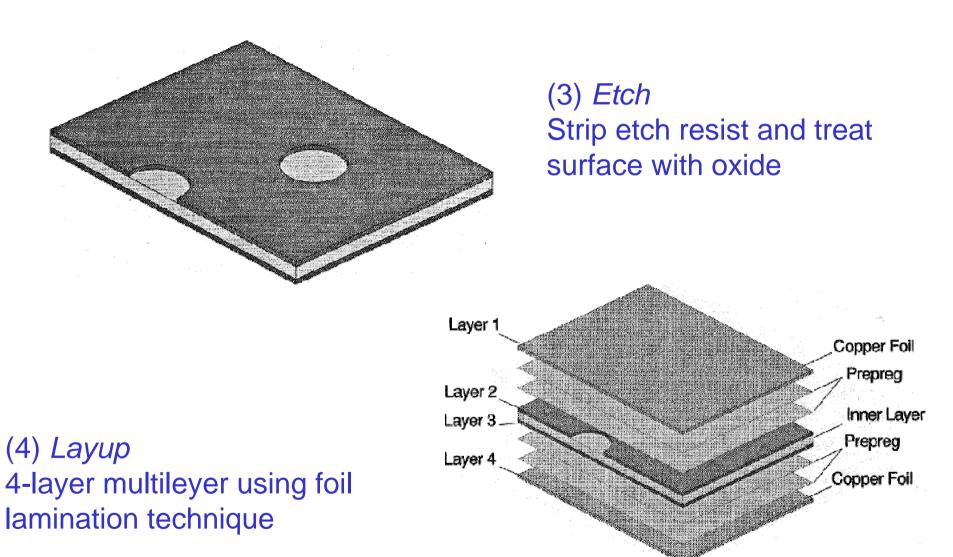

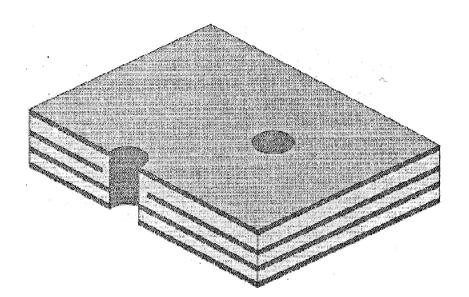

#### (5) Laminate

Heat and pressure cause prepreg to flow and bond layers together

# Hole sizes and location are determined

(6) Drill

**Technical University of Lodz**

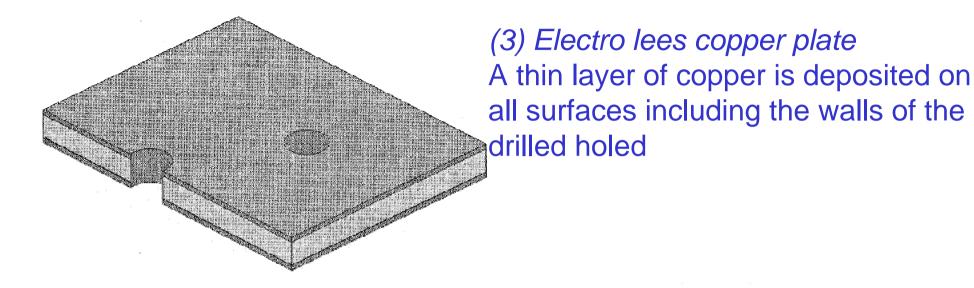

(7) Electroless copper plateA thin layer of copper is depositedfollowing smear removal, cleaning andpreparation

(8) Apply plating resistThe desired circuitry is left uncovered

**Technical University of Lodz**

(9) *Electroplate copper* The specified thickness is electrolytically deposited (usually 0.001")

(10) Electroplate etch resistTin or tin/lead is electrolyticallydeposited over the copper plating

Technical University of Lodz

(11) Strip plating resistPlating resist is chemically removed,revealing the copper surface

#### (12) Etch

The unwanted copper is removed chemically by an etchant that attacks copper, but not tin or tin/lead

Technical University of Lodz

**Department of Microelectronics and Computer Sciences**

28

(13) Strip etch resist The tin or tin/lead is chemically removed

# (14) Apply solder resist The specified resist (dry film, liquid photoimageable or screen printed) is applied to the surfaces of the PCB or panel

**Technical University of Lodz**

**Department of Microelectronics and Computer Sciences**

Solder Resist (Solder Mask)

(15) *Solder coat* Solder (tin/lead) is applied to the exposed copper areas and the excess solder is removed

#### **Technical University of Lodz**

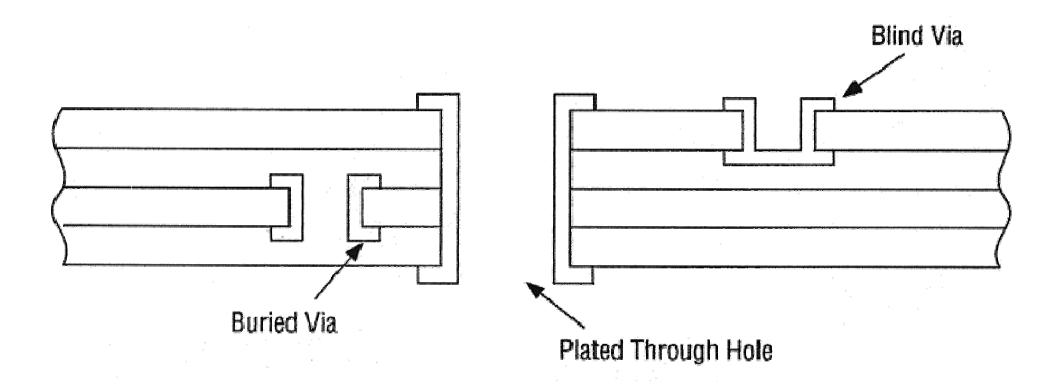

#### Through, blind and buried vias

#### **Technical University of Lodz**

# **Mounting technologies**

- Through-hole technology

- provides stronger mechanical bonds

- easy for design and modification (prototyping)

- limited routing area due to the holes

- expensive in mass-production

- Surface-mount technology

- Low cost in mass-production

- Smaller and more complex designs

#### **Technical University of Lodz**

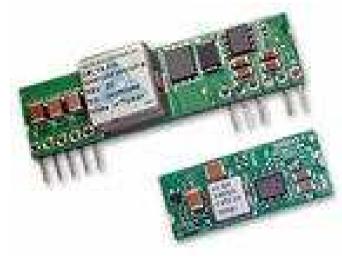

# Mounting technologies (special)

#### **Cordwood module**

Advantages: large space-saving Application: i.e. missile guidance and telemetry systems

#### Package

**Department of Microelectronics and Computer Sciences**

34

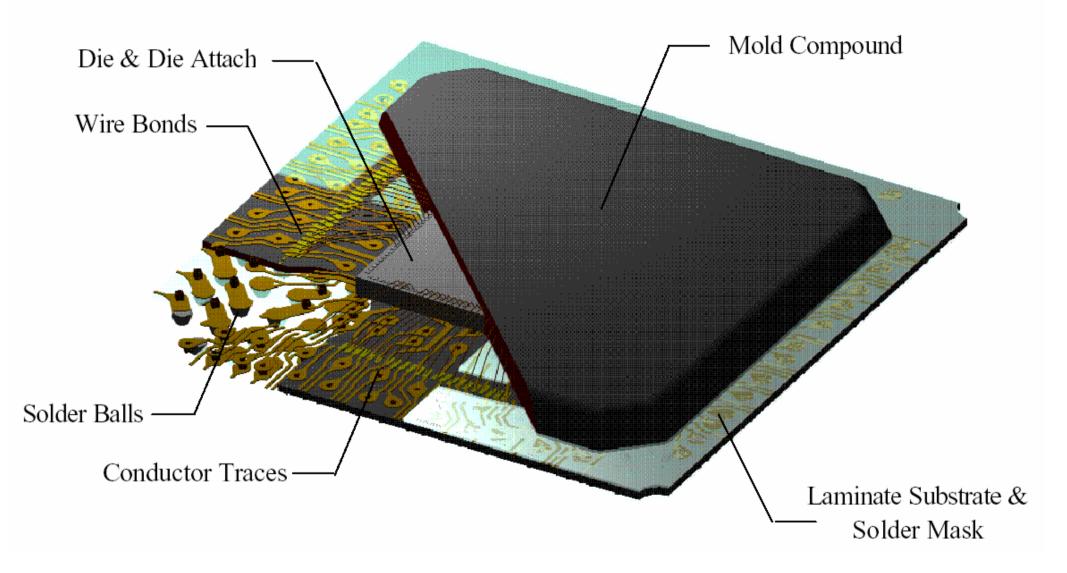

#### **Die interconnections**

#### **Technical University of Lodz**

## **Types of IC packages**

- Single in-line package (SIP)

- Dual In-line Package (DIP)

- Zig-zag in-line package (ZIP)

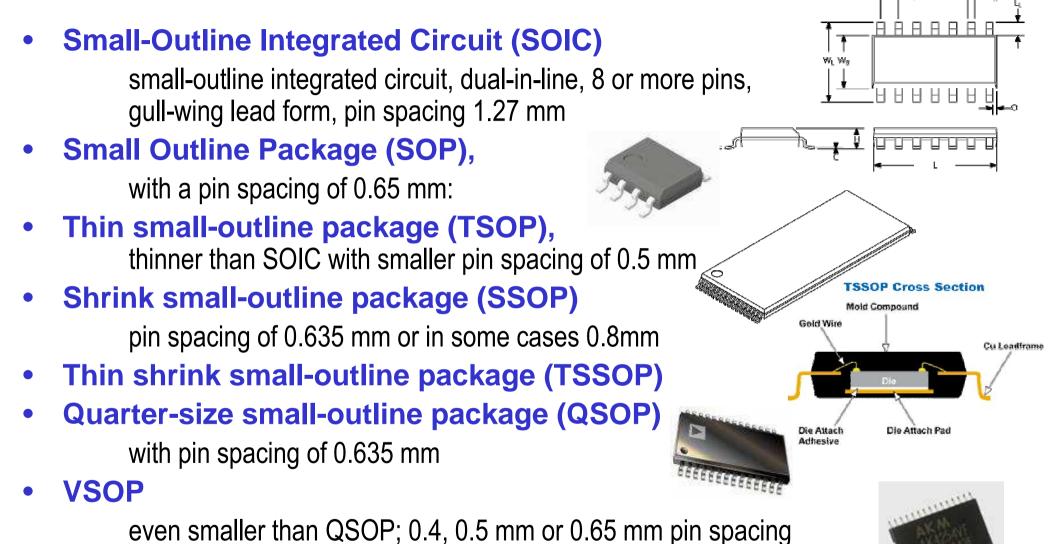

- Dual-in-line (SOIC, SOP, ....)

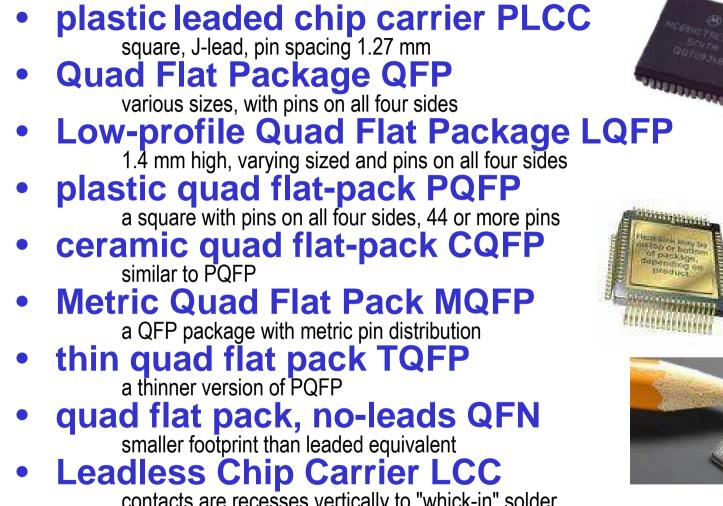

- Quad-in-line (PLCC, QFP, ...

- Grid arrays (PGA, BGA, CGA, others)

36

## Single in-line package (SIP)

SIP is an electronic device package with a rectangular housing and one row of electrical connecting pins

Currently the whole subsytsems might be encapsulated in SIP package

Technical University of Lodz

**Department of Microelectronics and Computer Sciences**

37

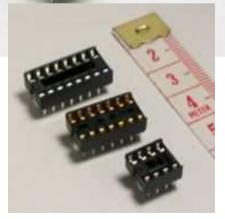

#### **Dual In-line Package (DIP)**

DIP (DIL) is an electronic device package with a rectangular housing and two parallel rows of electrical connecting pins, usually protruding from the longer sides of the package and bent downward.

The inter-lead spacing (lead pitch) is 0.1" (2.54 mm) and a row spacing is either 0.3 in (7.62 mm) or 0.6 in (15.24 mm).

DIPs were the mainstream of the microelectronics industry in the 1970s and 80s. Their use has subsided in recent years due to the emerging new surface-mount technology (SMT) packages such as PLCC and SOIC.

# Zig-zag in-line package (ZIP)

IC is encapsulated in a slab of plastic of dimension about 3 mm x 30 mm x 10 mm.

The package's pins protrude in two rows from one of the long edges (the rows are staggered by 1.27 mm (0.05"), giving them a zig-zag appearance)

This solution allowing them to be spaced more closely than a rectangular grid would allow.

The pins are inserted into holes in a printed circuit board, with the packages standing at right-angles to the board, allowing them to be placed closer together than DIPs of the same size.

Currently ZIPs have been superseded by surface-mount packages such as the thin small-outline packages (TSOPs) used on single-in-line memory modules (SIMMs) and dual-in-line memory modules (DIMMs).

**Technical University of Lodz** Department of Microelectronics and Computer Sciences

#### **Dual-in-line Packages**

Technical University of Lodz **Department of Microelectronics and Computer Sciences**

other

40

### **Quad-in-line packages**

contacts are recesses vertically to "whick-in" solder. Common in aviation electronics because of mechanical endurance against vibration.

#### others

#### **Grid array packages**

- Pin grid array (PGA)

- Ball grid array (BGA)

- with a square or rectangular array of solder balls on one surface, ball spacing typically 1.27 mm

- Low profile fine pitch BGA (LFBGA)

- with a square or rectangular array of solder balls on one surface, ball spacing typically 0.8 mm

- Column grid array CGA

- in which the input and output points are high temperature solder cylinders or columns arranged in a grid pattern.

- Ceramic column grid array CCGA

- in which the input and output points are high temperature solder cylinders or columns arranged in a grid pattern. The body of the component is ceramic.

- micro-BGA µBGA,

with ball spacing less than 1 mm

• Lead Less Package LLP

with metric pin distribution (0.5 mm pitch).

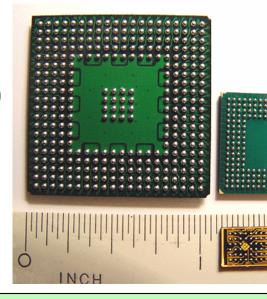

#### **Pin Grid Array PGA**

- The IC is mounted in a ceramic slab

- one face is covered, or partially covered, in a square array of metal pins.

- The space between pins is 2.54 mm (a tenth of an inch)

- The pins can then be inserted into the holes in a printed circuit board and soldered in place.

#### Advantages:

Less space occupation than older types such as the DIP.

Technical University of Lodz

From Computer Desktop Encyclopedia 3 2001 The Computer Language Co. Inc

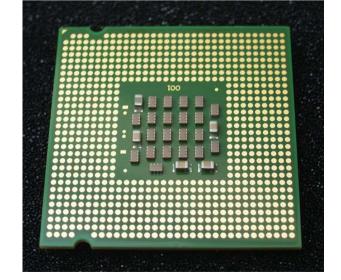

### **Ball Grid Arrays BGA**

The pins are replaced by balls of solder stuck to the bottom of the package.

#### Mounting:

The device is placed on a PCB that carries copper pads in a pattern that matches the solder balls. The assembly is then heated, either in a reflow oven or by an infrared heater, causing the solder balls to melt. Surface tension causes the molten solder to hold the package in alignment with the circuit board, at the correct separation distance, while

the solder cools and solidifies.

### Advantages:

- high density, no problems with soldering

- good heat conduction (good contact with PCB)

- Low connection inductance

#### Disadvantages

•Share stresses between BGA and PCB •Hard inspection

#### **Technical University of Lodz**

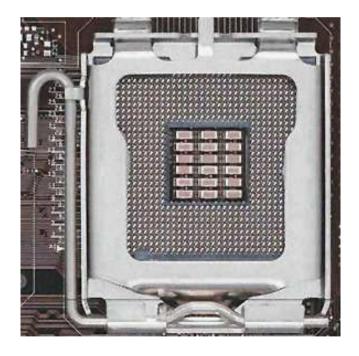

#### Land Grid Array LGA

- Similar to Pin Grid Array but there are no pins on the chip;

- in place of the pins are **pads** of bare gold-plated copper that touch pins on the motherboard.

## **Application:**

Intel Pentium 4, Intel Xeon, Intel Core 2 and AMD Opteron families

#### Technical University of Lodz

**Department of Microelectronics and Computer Sciences**

45

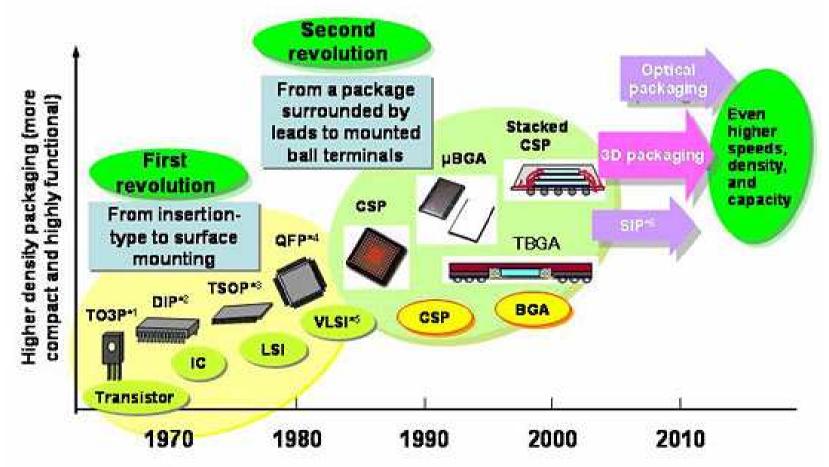

#### **Trends in IC packaging**

Trends in High-Density Semiconductor Packaging 🏾 🖌

<sup>™</sup>TO-3P (name of a typical transistor package) <sup>™</sup>DIP (Dual In-line Package) <sup>™</sup>TSOP (Thin Small Outline Package) <sup>™</sup>GFP (Quad Flat Package) <sup>™</sup>VLSI (Very Large Scale Integration) <sup>™</sup>SIP (System In Package)

HITACHI

3-7)

From http://www.hitachi-cable.co.jp webpage

@ 2005 Hitachi Cable, Ltd.

**Technical University of Lodz**

47

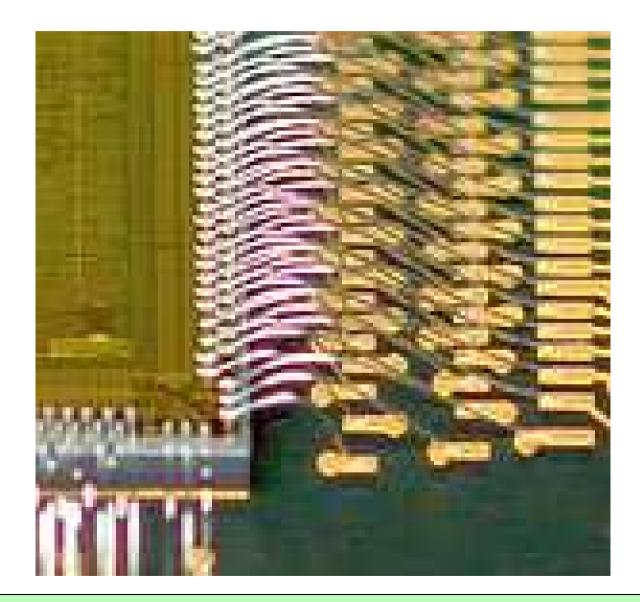

#### Non-packaged device

- surface mount, (require specific process for assembly)

- Types of non-packaged devices:

- chip-on-board (COB)

a bare silicon chip, that is usually an integrated circuit, is supplied without a package and is attached, often with epoxy, directly to a circuit board. The chip is then wire bonded and protected from mechanical damage and contamination by an epoxy "glob-top".

– chip-on-flex (COF)

as before, but a chip is mounted directly to a flex circuit.

– chip-on-glass (COG)

as COB, but chip is mounted directly to a piece of glass - typically an *LCD display*

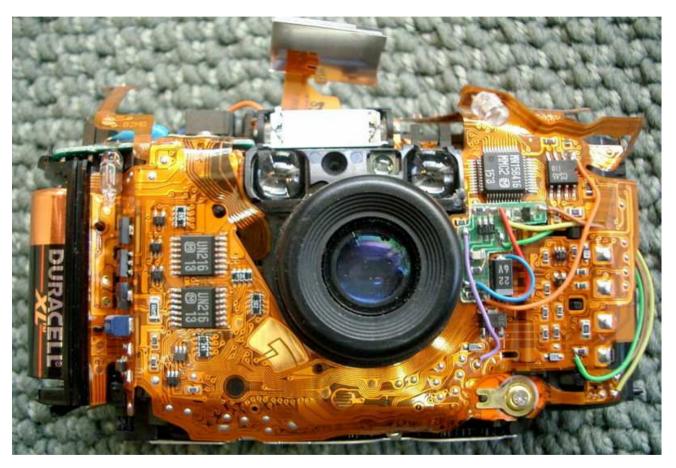

#### Flex circuit assembling

It is not rare to use flex circuits ....

Olympus Stylus camera with skins removed, showing flex circuit assembly

from wikipedia.org

**Technical University of Lodz**

49

# Thank you for your attention

**Technical University of Lodz**

#### **Technical University of Lodz**