## Electronic Technology Design and Workshop

Presented and updated by

Przemek Sekalski DMCS room 2

2007

**Technical University of Lodz**

## Electronic Technology Design and Workshop

## Lecture 7 Electronic Circuit Synthesis

Technical University of Lodz

## **Synthesis of electronic circuits**

**Technical University of Lodz**

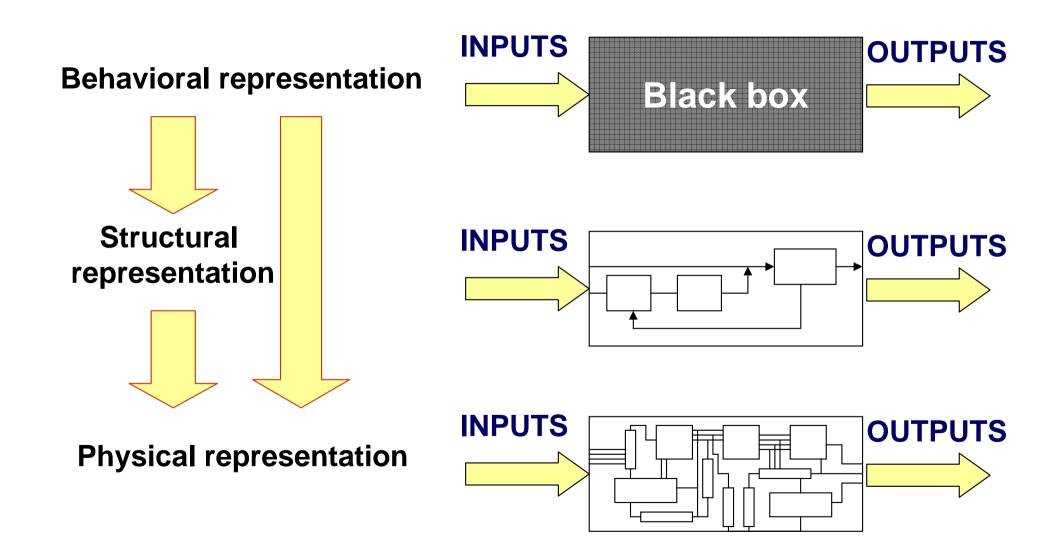

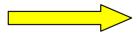

## Synthesis of digital electronic circuits

Automatic translation of the circuit description to less abstract representations e.g.

- a) from behavioural to structural

- b) from structural to physical

- c) from behavioural to physical

| nysicai    | behavioral | structural | physical |

|------------|------------|------------|----------|

| Transistor |            |            |          |

| Gate       |            |            |          |

| Register   |            |            |          |

| Processor  |            |            |          |

Not supported

(some support possible in specific cases - software-hardware codesign)

Partially supported (fully supported for certain types of digital designs)

Fully supported

**Technical University of Lodz** Department of Microelectronics and Computer Sciences

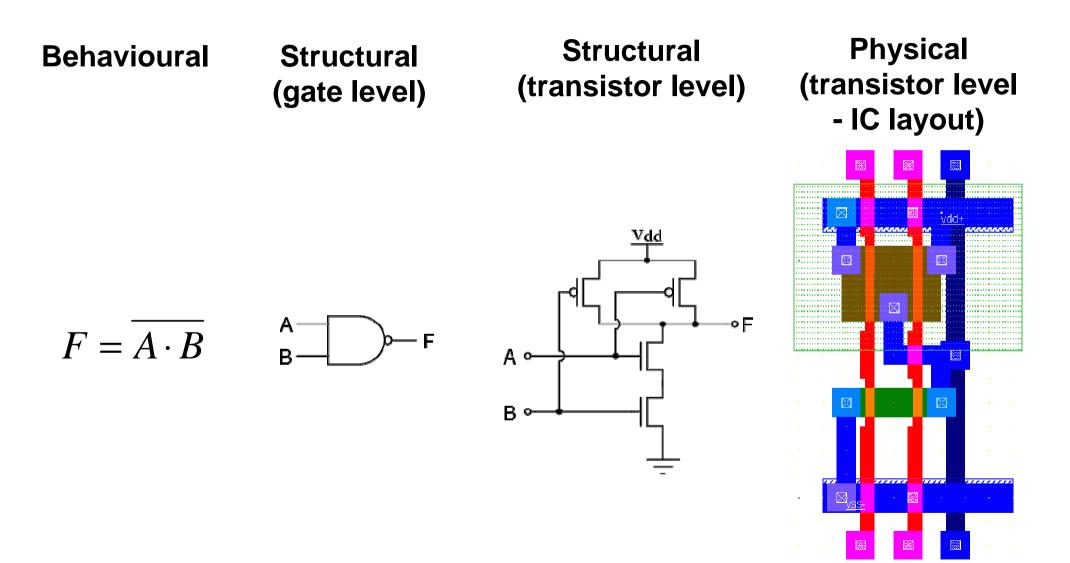

### **Digital synthesis**

#### **Technical University of Lodz**

## **Digital synthesis with PLD**

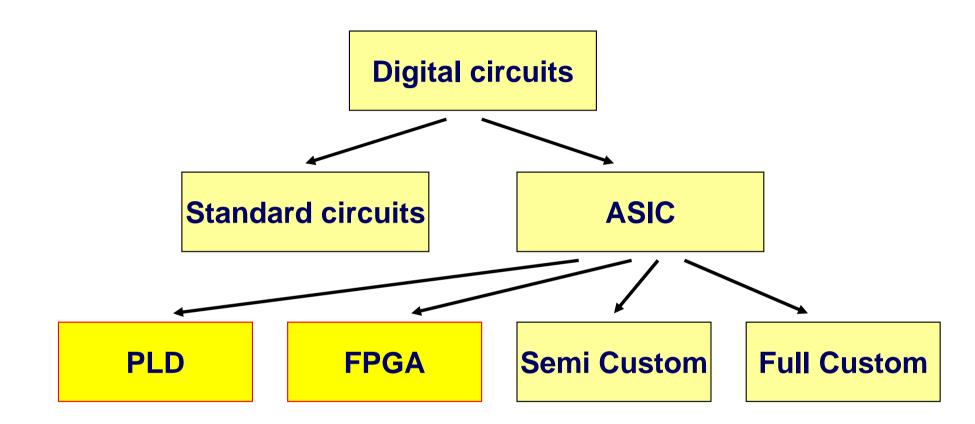

### **Digital circuits classification**

ASIC - Application Specific Integrated Circuit

PLD - Programmable Logic Device

FPGA - Field Programmable Gate Array

Semi Custom - Integrated Circuits designed by users with library cells

Full Custom - Integrated Circuits dsigned from scratch, designed or orderd by users

**Technical University of Lodz**

8

## **Digital circuits description languages**

**ABEL** (Advanced Boolean Expression Language) one of the oldest HDL, applicable for simple and less complex digital circuits, originally designed for programming certain types of PLDs, projects can be described by Boolean equations, truth tables or state-diagrams.

**VHDL** - Very High Speed Integrated Circuit (*VHSIC*) Hardware Description Language language for general description of complex digital circuits, acknowledged as IEEE standard (1987), designed for uniform documentation and simulation of digital projects, not targeted for any specific architecture, allows the description of parallel and sequential processing

#### Verilog -

most popular industry standard, acknowledged as IEEE standard (1995) less complex than VHDL and easier to learn, based on C-language structure, best suited for complex FPGA circuits

#### **Example of behavioral description**

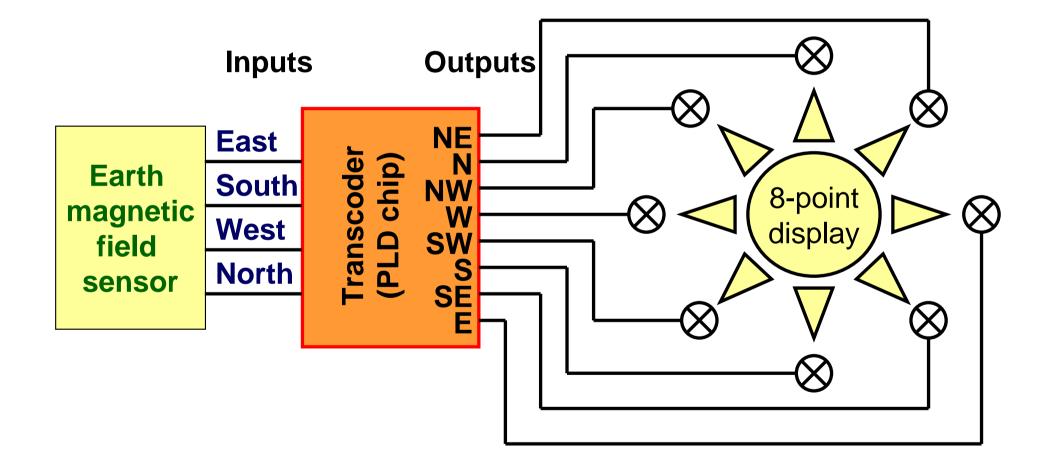

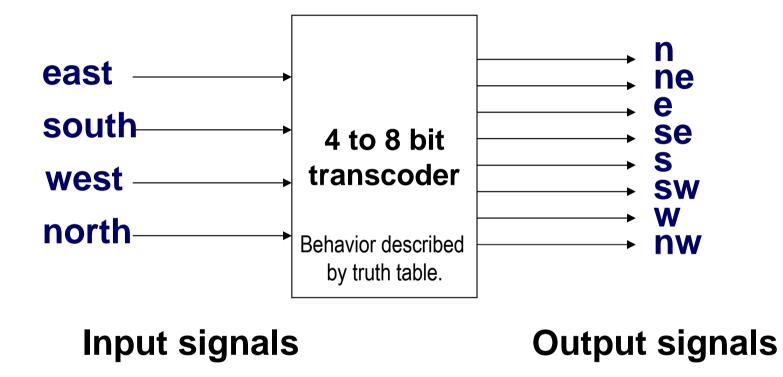

#### **Electronic Compass**

**Technical University of Lodz**

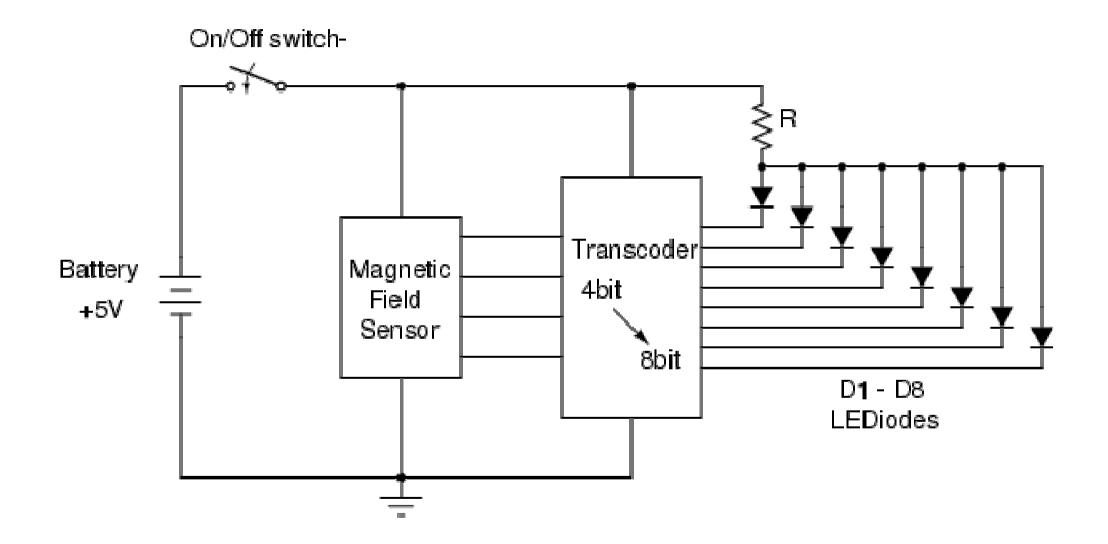

#### **Electronic Compass - schematic**

**Technical University of Lodz**

#### **Electronic Compass - transcoder truth-table**

|       | Inp  | uts  |       |   |    |   | Out | puts |    |   |    |

|-------|------|------|-------|---|----|---|-----|------|----|---|----|

| North | West | East | South | Ν | NE | Ε | SE  | S    | SW | W | NW |

| 0     | 1    | 1    | 1     | 0 | 1  | 1 | 1   | 1    | 1  | 1 | 1  |

| 0     | 1    | 0    | 1     | 1 | 0  | 1 | 1   | 1    | 1  | 1 | 1  |

| 1     | 1    | 0    | 1     | 1 | 1  | 0 | 1   | 1    | 1  | 1 | 1  |

| 1     | 1    | 0    | 0     | 1 | 1  | 1 | 0   | 1    | 1  | 1 | 1  |

| 1     | 1    | 1    | 0     | 1 | 1  | 1 | 1   | 0    | 1  | 1 | 1  |

| 1     | 0    | 1    | 0     | 1 | 1  | 1 | 1   | 1    | 0  | 1 | 1  |

| 1     | 0    | 1    | 1     | 1 | 1  | 1 | 1   | 1    | 1  | 0 | 1  |

| 0     | 0    | 1    | 1     | 1 | 1  | 1 | 1   | 1    | 1  | 1 | 0  |

**Technical University of Lodz**

#### **Electronic Compass – transcoder chip**

## The ABEL code (part I)

module transcoder; title '4 to 8 bit transcoder for electronic comapss'

transcoder device 'P16H8';

north, west, east, south pin; n, ne, e, se, s, sw, w, nw pin istype 'com';

on = 0; off = 1;

yes = 0; no = 1; **Beginning of the ABEL program**

Declarations of input and output signals (similar to variables in programming languages)

Definitions of constants (in order to improve clarity of the program)

## The ABEL code (part II)

truth\_table

####

#### test\_vectors

Behavioral description of the device functionality (here in form of truth-table)

# Verification of correctness of generated equations

#### Technical University of Lodz

#### The code implementation

#### Automatically generated equations:

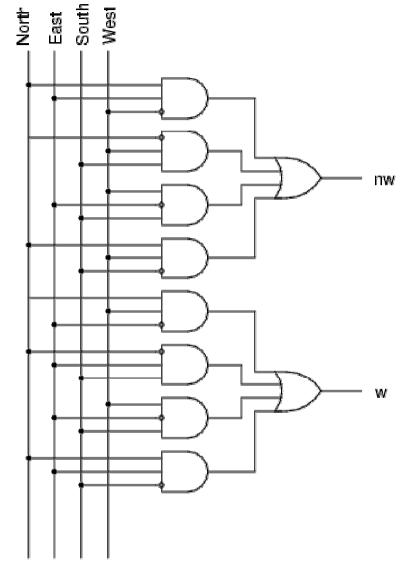

nw = (north & !west & east # !north & west & south # west & !east & south # north & west & !south);

w = (north & west & !east # !north & east & south # west & !east & south # north & east & !south);

#### Automatically generated logical structure

. . .

. . .

. . .

## P16H8 Chip Diagram

4 to 8 bit transcoder for electronic comapss

| -     | +  | -\ | F   |

|-------|----|----|-----|

|       |    | \/ |     |

| north | 1  | 20 | Vcc |

| west  | 2  | 19 | n   |

| east  | 3  | 18 | е   |

| south | 4  | 17 | se  |

|       | 5  | 16 | S   |

|       | 6  | 15 | SW  |

|       | 7  | 14 | w   |

|       | 8  | 13 | nw  |

|       | 9  | 12 | ne  |

| GND   | 10 | 11 |     |

|       |    |    |     |

**Technical University of Lodz**

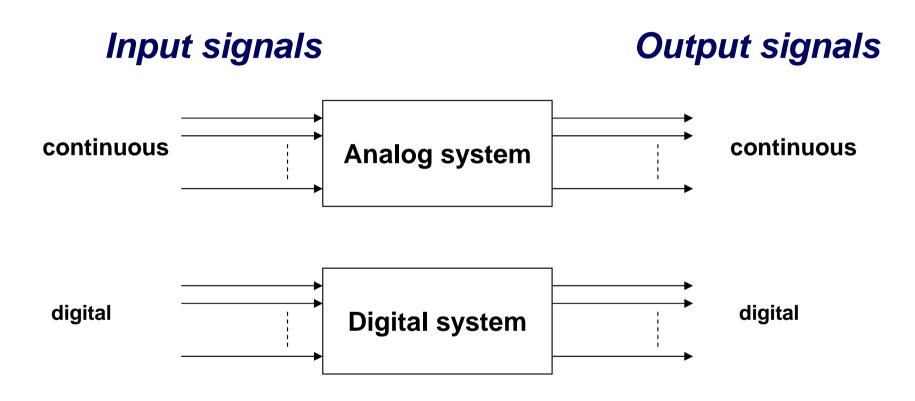

#### **Digital vs Analog Systems**

Technical University of Lodz

#### **Boolean Algebra**

Identity element Commutativity Associativity Distributivity Complement

a+0=a a+b=b+a a+(b+c)=(a+b)+c a+(b\*c)=(a+b)\*(a+c) a+ā=1 a\*1=a a\*b=b\*a a\*(b\*c)=(a\*b)\*c a\*(b+c)=(a\*b)+(a\*c) a\*ā=0

Idempotency Complement Absorption Element Elimination De Morgan's Laws a+a=aa+1=1a+a\*b=a $a+\bar{a}*b=a+b$  $\overline{a+b}=\bar{a}*\bar{b}$   $a^*a=a$   $a^*0=0$   $a^*(a+b)=a$   $a^*(\bar{a}+b)=a^*b$  $\bar{a}^*b=\bar{a}+\bar{b}$

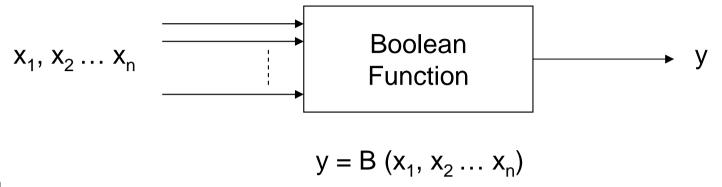

#### **Boolean Functions**

E.g.

$$f(a, b, c) = a^*(b+\bar{c}) + (\bar{a}+b)^*c$$

#### **Truth Table notation**

| а | b | С | f(a, b, c) |

|---|---|---|------------|

| 0 | 0 | 0 | 0          |

| 0 | 0 | 1 | 1          |

| 0 | 1 | 0 | 0          |

| 0 | 1 | 1 | 1          |

| 1 | 0 | 0 | 1          |

| 1 | 0 | 1 | 0          |

| 1 | 1 | 0 | 1          |

| 1 | 1 | 1 | 1          |

#### **Minterm notation**

$$f(a, b, c) = \bar{a}\bar{b}c + \bar{a}bc + a\bar{b}\bar{c} + ab\bar{c} + abc$$

#### **Maxterm notation**

$$f(a, b, c) = (a+b+c) (a+\bar{b}+c) (\bar{a}+b+\bar{c})$$

19

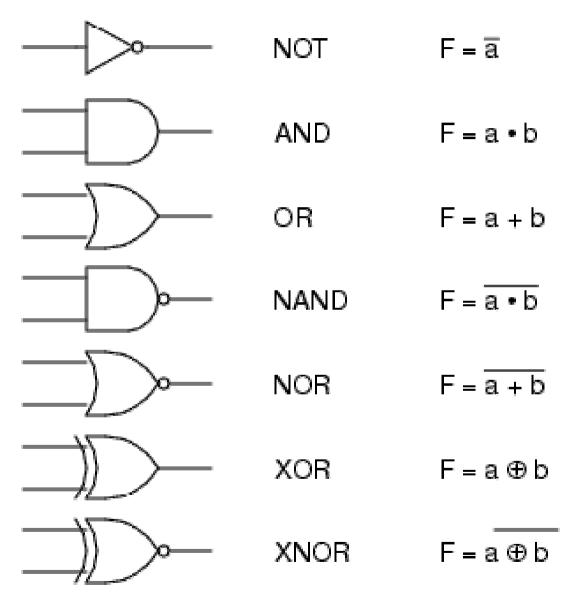

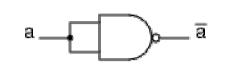

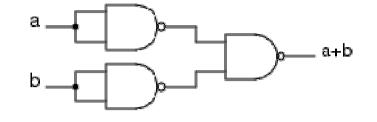

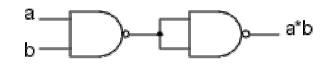

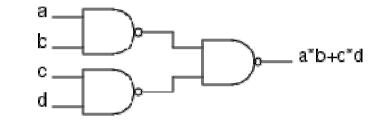

#### **Logic Gates**

Technical University of Lodz

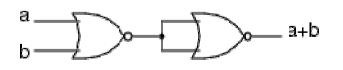

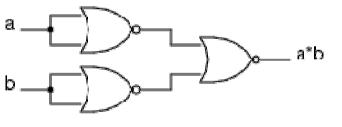

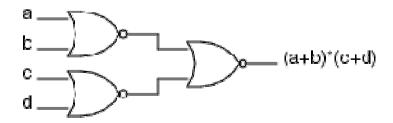

#### **Boolean Function Realization - examples**

#### **Technical University of Lodz**

## **Memory Elements (flip-flops)**

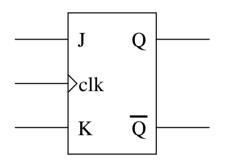

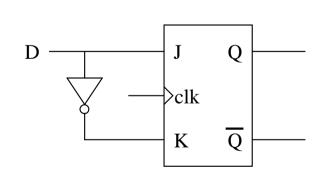

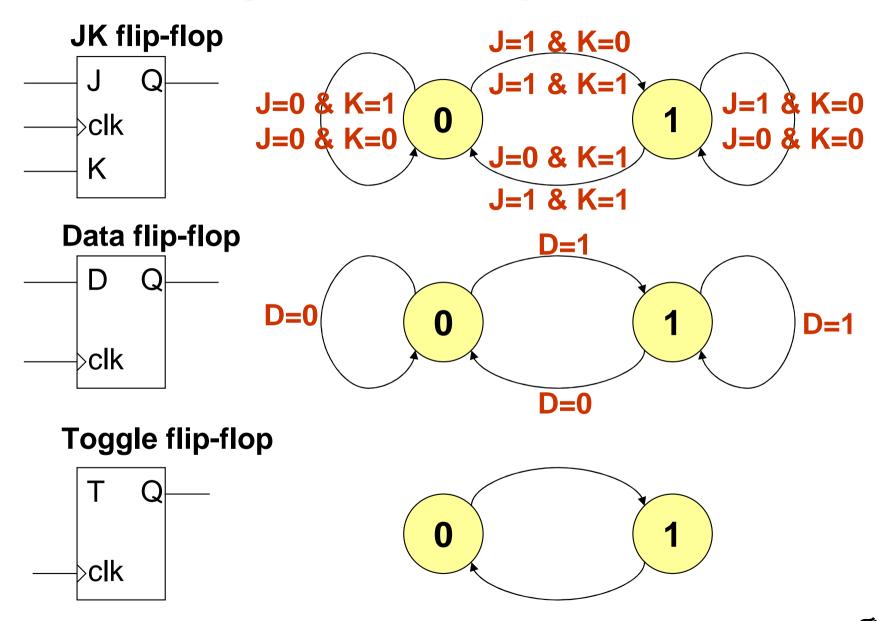

#### JK flip-flop

| J(t) | K(t) | Q(t+1)            |

|------|------|-------------------|

| 0    | 0    | Q(t)              |

| 0    | 1    | 0                 |

| 1    | 0    | _1                |

| 1    | 1    | $\overline{Q}(t)$ |

$Q(t+1) = J(t) \ \overline{Q}(t) + \overline{K}(t) \ Q(t)$

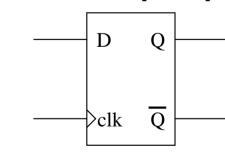

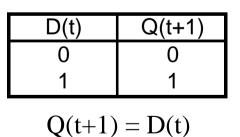

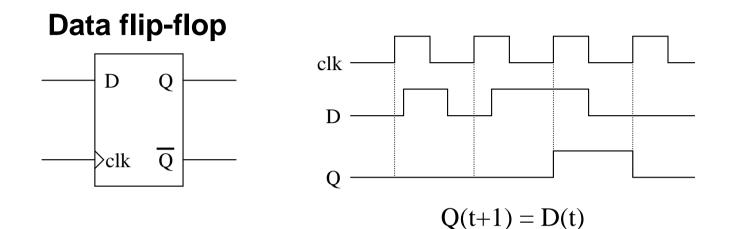

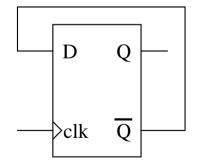

#### Data flip-flop

## **Memory Elements (flip-flops)**

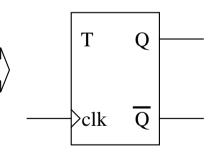

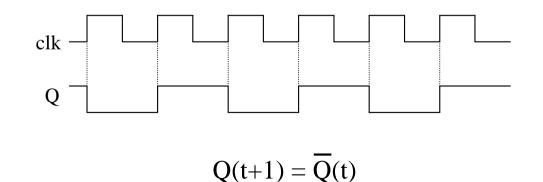

Toggle flip-flop

Technical University of Lodz

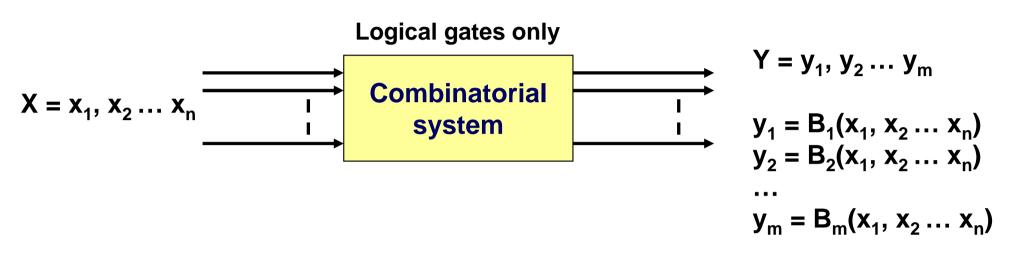

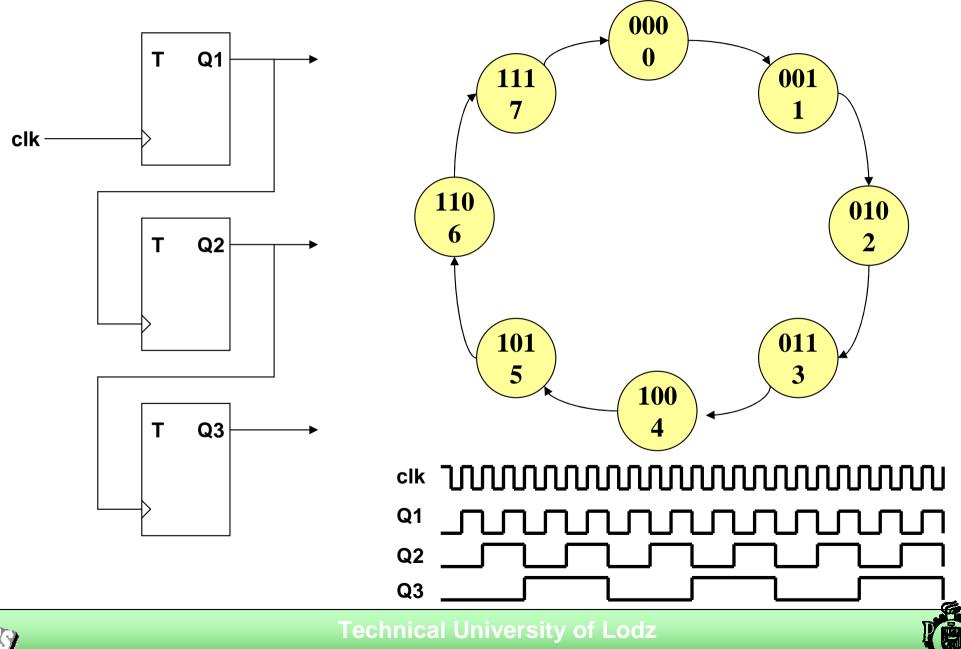

### **Digital Systems**

Y = B(X)

Any change of input signals causes the appropriate change of output signals, as fast as it is possible, i.e after the propagation time of logical gates.

Output signals in combinatorial circuits depends only on the present input signals.

B<sub>x</sub> - boolean function

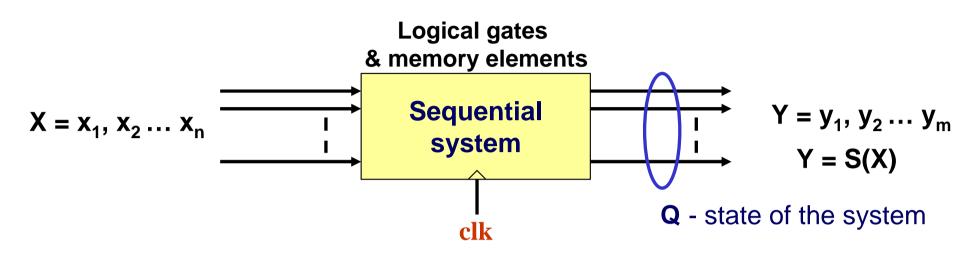

#### **Digital Systems**

Output signals are the outputs of memory elements and they may change only after a new write operation is performed.

Output signals are Boolean functions (S) of input signals, but they may change only at prescribed moments.

When there is no write (store) operation, the output remains stable, regardless the state of the input signals.

The sufficient description of the sequential system is given by the set of signals at the output of the memory elements, i.e. *state of the system (Q)*

**Technical University of Lodz** Department of Microelectronics and Computer Sciences

25

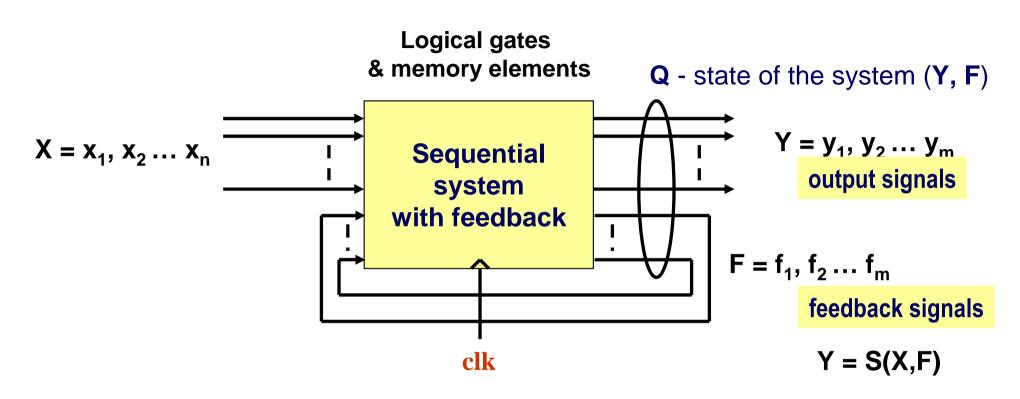

### **Digital Systems**

Output signals are boolean functions (S) of input signals and feedback signals, but they may change only at prescribed moments.

The sufficient description of the sequential system is given by the set of signals at the output of the memory elements, i.e. *state of the system (Q) - output & feedback*

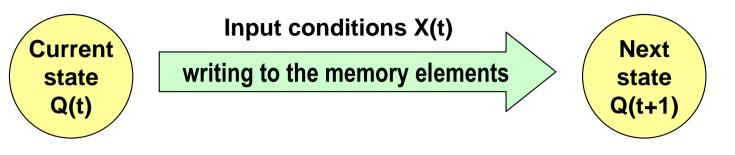

## **Description of Sequential Digital Systems**

What the next state will be after the transition depends on1) the current state (values of the memory element signals Y, F)2) the values of input signals at the moment of the transition

**Technical University of Lodz**

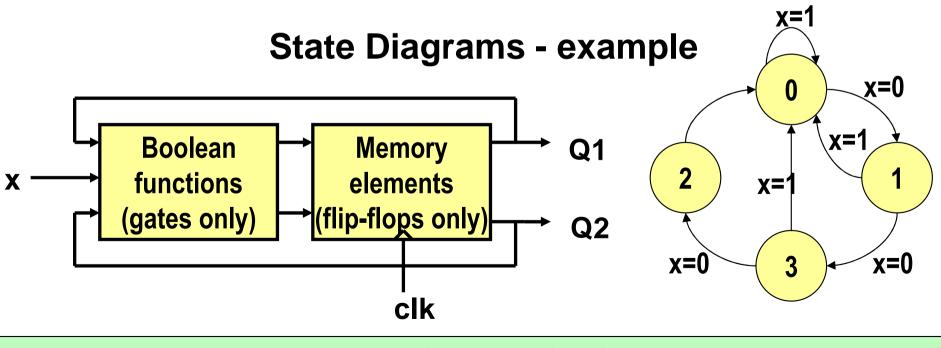

#### **State Diagrams – memory elements**

**Technical University of Lodz**

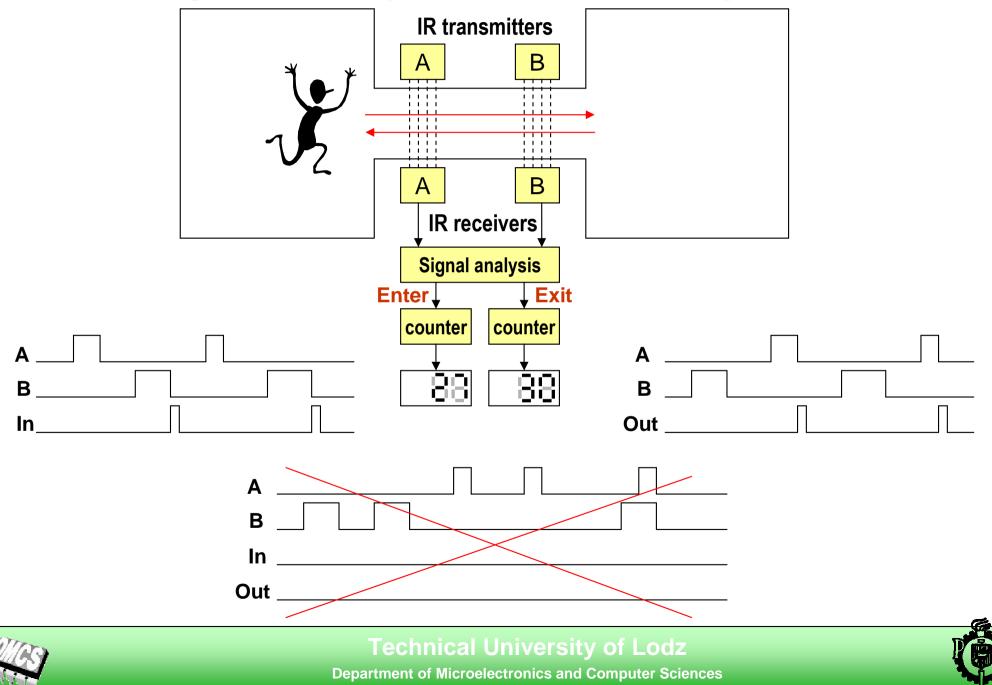

#### State Diagram example - bi-directional person counter

#### **State Diagram example - bi-directional person counter**

#### **Technical University of Lodz**

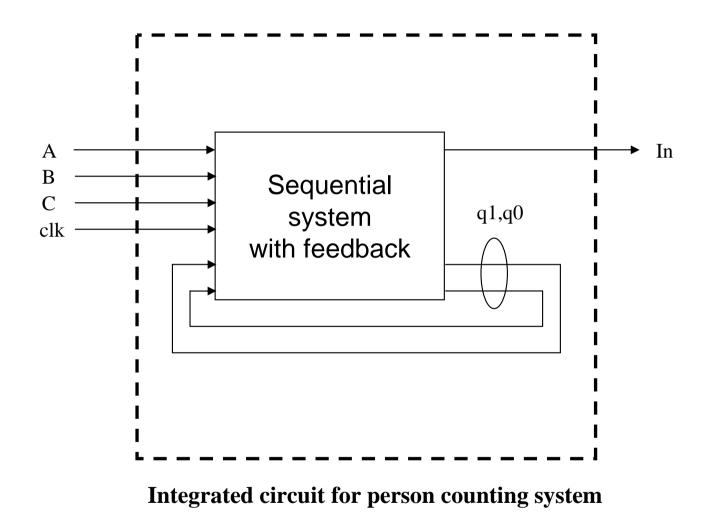

#### **Realization - uni-directional person counter**

Technical University of Lodz

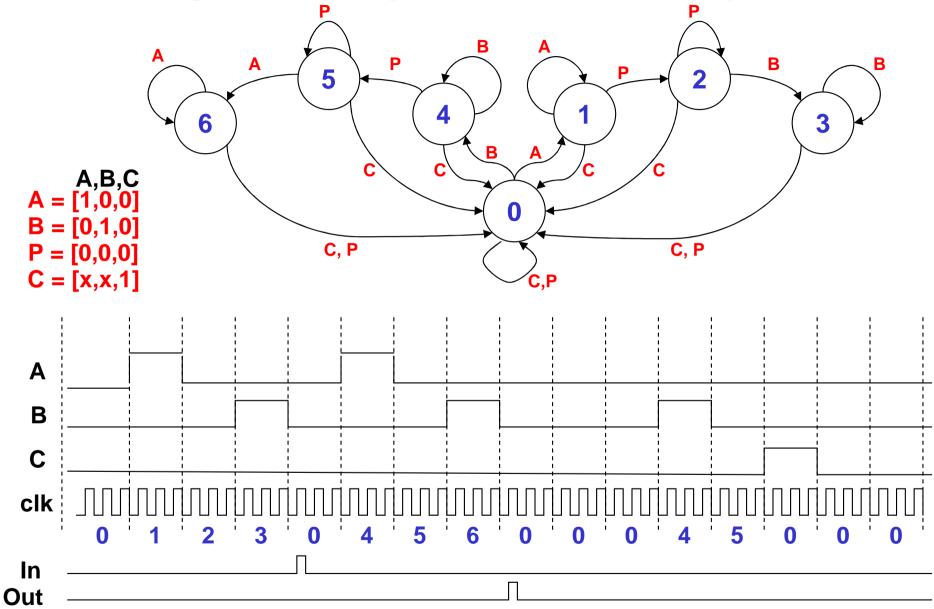

## **ABEL - bi-directional person counter**

module pcounter; title 'Bi-direction person counter'

> clk pin; "clock signal A,B pin; "signals from IR sensors C pin; "clear signal

In\_ pin istype 'reg'; "output line

q1,q0 node istype 'reg'; "state counter

C = .C.; X = .X.;

Equations

[q1..q0].clk=clk; In\_.clk=clk; State\_Diagram [q1..q0] state 0:if ((A==1) & (B==0) & (C==0)) then 1 with In\_:=0 else 0 with In\_:=0;

state 1:if (C==1) then 0 else if ((A==1) & (B==0)) then 1 else if ((A==0) & (B==0)) then 2;

state 2:if (C==1) then 0 else if ((A==0) & (B==0)) then 2 else if ((A==0) & (B==1)) then 3;

state 3:if ((A==0) & (B==1)) then 3 else 0 with In\_:=1;

end pcounter;

#### **ABEL - bi-directional person counter**

test\_vectors ([clk,A,B,C] -> [q1,q0,ln\_]) [ c,0,0,0] -> [ 0, 0, 0]; [ c,1,0,0] -> [ 0, 1, 0]; [ c,0,0,0] -> [ 1, 0, 0]; [ c,0,1,0] -> [ 1, 1, 0]; [ c,0,0,0] -> [ 0, 0, 1]; [ c,0,0,0] -> [ 0, 0, 0]; [ c,1,0,0] -> [ 0, 1, 0]; [ c,x,x,1] -> [ 0, 0, 0]; [ c,0,0,0] -> [ 0, 0, 0]; [ 0,1,0,0] -> [ 0, 1, 0]; [ c,1,0,0] -> [ 0, 1, 0];

Equations:

In\_:= (!B & q1.FB & q0.FB # A & q1.FB & q0.FB);

$In\_.C = (clk);$

q0 := (!A & B & q1.FB & q0.FB # !A & B & !C & q1.FB # A & !B & !C & !q1.FB);

q0.C = (clk);

q1 := (!A & B & q1.FB & q0.FB # !A & !C & q1.FB & !q0.FB # !A & !B & !C & !q1.FB & q0.FB);

q1.C = (clk);

34