# **APEX 20K**

Programmable Logic Device Family

### April 2001, ver. 3.6

| Features ■                  | <ul> <li>Industry's first programmable logic device (PLD) incorporating system-on-a-programmable-chip (SOPC) integration</li> <li>MultiCore<sup>™</sup> architecture integrating look-up table (LUT) logic, product-term logic, and embedded memory</li> <li>LUT logic used for register-intensive functions</li> <li>Embedded system block (ESB) used to implement memory functions, including first-in first-out (FIFO) buffers, dual-port RAM, and content-addressable memory (CAM)</li> <li>ESB implementation of product-term logic used for combinatorial-intensive functions</li> </ul> |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | High density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                             | <ul> <li>30,000 to 1.5 million typical gates (see Tables 1 and 2)</li> <li>Up to 51,840 logic elements (LEs)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                             | <ul> <li>Up to 442,368 RAM bits that can be used without reducing available logic</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                             | - Up to 3,456 product-term-based macrocells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Table 1 APEX 20K Device Fea | atures Note (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Table T. APEX 20K Device realules Note (1) |          |          |          |           |           |          |           |  |  |

|--------------------------------------------|----------|----------|----------|-----------|-----------|----------|-----------|--|--|

| Feature                                    | EP20K30E | EP20K60E | EP20K100 | EP20K100E | EP20K160E | EP20K200 | EP20K200E |  |  |

| Maximum<br>system<br>gates                 | 113,000  | 162,000  | 263,000  | 263,000   | 404,000   | 526,000  | 526,000   |  |  |

| Typical<br>gates                           | 30,000   | 60,000   | 100,000  | 100,000   | 160,000   | 200,000  | 200,000   |  |  |

| LEs                                        | 1,200    | 2,560    | 4,160    | 4,160     | 6,400     | 8,320    | 8,320     |  |  |

| ESBs                                       | 12       | 16       | 26       | 26        | 40        | 52       | 52        |  |  |

| Maximum<br>RAM bits                        | 24,576   | 32,768   | 53,248   | 53,248    | 81,920    | 106,496  | 106,496   |  |  |

| Maximum<br>macrocells                      | 192      | 256      | 416      | 416       | 640       | 832      | 832       |  |  |

| Maximum<br>user I/O<br>pins                | 128      | 196      | 252      | 246       | 316       | 382      | 376       |  |  |

| Table 2. APEX 20K Device Features     Note (1) |           |           |           |           |            |            |  |  |  |  |

|------------------------------------------------|-----------|-----------|-----------|-----------|------------|------------|--|--|--|--|

| Feature                                        | EP20K300E | EP20K400  | EP20K400E | EP20K600E | EP20K1000E | EP20K1500E |  |  |  |  |

| Maximum<br>system gates                        | 728,000   | 1,052,000 | 1,052,000 | 1,537,000 | 1,772,000  | 2,392,000  |  |  |  |  |

| Typical gates                                  | 300,000   | 400,000   | 400,000   | 600,000   | 1,000,000  | 1,500,000  |  |  |  |  |

| LEs                                            | 11,520    | 16,640    | 16,640    | 24,320    | 38,400     | 51,840     |  |  |  |  |

| ESBs                                           | 72        | 104       | 104       | 152       | 160        | 216        |  |  |  |  |

| Maximum<br>RAM bits                            | 147,456   | 212,992   | 212,992   | 311,296   | 327,680    | 442,368    |  |  |  |  |

| Maximum<br>macrocells                          | 1,152     | 1,664     | 1,664     | 2,432     | 2,560      | 3,456      |  |  |  |  |

| Maximum user<br>I/O pins                       | 408       | 502       | 488       | 588       | 708        | 808        |  |  |  |  |

#### Note to tables:

(1) The embedded IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan circuitry contributes up to 57,000 additional gates.

# ...and More Features

- Designed for low-power operation

- 1.8-V and 2.5-V supply voltage (see Table 3)

- MultiVolt<sup>™</sup> I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- ESB offering programmable power-saving mode

| Feature                                                     | De                               | vice                                                                                                                           |

|-------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                                                             | EP20K100<br>EP20K200<br>EP20K400 | EP20K30E<br>EP20K60E<br>EP20K100E<br>EP20K160E<br>EP20K200E<br>EP20K300E<br>EP20K400E<br>EP20K600E<br>EP20K1000E<br>EP20K1500E |

| Internal supply voltage (V <sub>CCINT</sub> )               | 2.5 V                            | 1.8 V                                                                                                                          |

| MultiVolt I/O interface voltage levels (V <sub>CCIO</sub> ) | 2.5 V, 3.3 V, 5.0 V (1)          | 1.8 V, 2.5 V, 3.3 V,<br>5.0 V <i>(</i> 2 <i>)</i>                                                                              |

#### Notes:

- (1) Certain APEX 20K devices are 5.0-V tolerant. See "MultiVolt I/O Interface" on page 46 for details.

- (2) APEX 20KE devices can be 5.0-V tolerant by using an external resistor.

- Flexible clock management circuitry with up to four phase-locked loops (PLLs)

- Built-in low-skew clock tree

- Up to eight global clock signals

- ClockLock<sup>TM</sup> feature reducing clock delay and skew

- ClockBoost<sup>™</sup> feature providing clock multiplication and division

- ClockShift<sup>™</sup> programmable clock phase and delay shifting

- Powerful I/O features

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2* for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Support for high-speed external memories, including DDR SDRAM and ZBT SRAM (ZBT is a trademark of Integrated Device Technology, Inc.)

- Bidirectional I/O performance  $(t_{CO} + t_{SU})$  up to 250 MHz

- LVDS performance up to 840 Mbits per channel

- Direct connection from I/O pins to local interconnect providing fast t<sub>CO</sub> and t<sub>SU</sub> times for complex logic

- MultiVolt I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- Programmable clamp to V<sub>CCIO</sub>

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Support for advanced I/O standards, including low-voltage differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, stubseries terminated logic (SSTL-3 and SSTL-2), Gunning transceiver logic plus (GTL+), and high-speed terminated logic (HSTL Class I)

- Hot-socketing support in APEX 20KE devices

- Pull-up on I/O pins before and during configuration

- Advanced interconnect structure

- Four-level hierarchical FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

- Advanced packaging options

- Available in a variety of packages with 144 to 1,020 pins (see Tables 4 through 7)

- FineLine BGA<sup>™</sup> packages maximize board space efficiency

### Advanced software support

- Software design support and automatic place-and-route provided by the Altera<sup>®</sup> Quartus<sup>™</sup> II development system for Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations

- Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- NativeLink<sup>TM</sup> integration with popular synthesis, simulation, and timing analysis tools

- Quartus II SignalTap<sup>™</sup> embedded logic analyzer simplifies in-system design evaluation by giving access to internal nodes during device operation

- Supports popular revision-control software packages including PVCS, Revision Control System (RCS), and Source Code Control System (SCCS)

| Table 4. APEX 20K | QFP, BGA & PG   | A Package Op            | tions & I/O Co          | unt Notes (1 | 1), (2)     |             |

|-------------------|-----------------|-------------------------|-------------------------|--------------|-------------|-------------|

| Device            | 144-Pin<br>TQFP | 208-Pin<br>PQFP<br>RQFP | 240-Pin<br>PQFP<br>RQFP | 356-Pin BGA  | 652-Pin BGA | 655-Pin PGA |

| EP20K30E          | 92              | 125                     |                         |              |             |             |

| EP20K60E          | 92              | 148                     | 151                     | 196          |             |             |

| EP20K100          | 101             | 159                     | 189                     | 252          |             |             |

| EP20K100E         | 92              | 151                     | 183                     | 246          |             |             |

| EP20K160E         | 88              | 143                     | 175                     | 271          |             |             |

| EP20K200          |                 | 144                     | 174                     | 277          |             |             |

| EP20K200E         |                 | 136                     | 168                     | 271          | 376         |             |

| EP20K300E         |                 |                         | 152                     |              | 408         |             |

| EP20K400          |                 |                         |                         |              | 502         | 502         |

| EP20K400E         |                 |                         |                         |              | 488         |             |

| EP20K600E         |                 |                         |                         |              | 488         |             |

| EP20K1000E        |                 |                         |                         |              | 488         |             |

| EP20K1500E        |                 |                         |                         |              | 488         |             |

| Device     | 144 Pin | 324 Pin | 484 Pin | 672 Pin | 1,020 Pin |

|------------|---------|---------|---------|---------|-----------|

| EP20K30E   | 93      | 128     |         |         |           |

| EP20K60E   | 93      | 196     |         |         |           |

| EP20K100   |         | 252     |         |         |           |

| EP20K100E  | 93      | 246     |         |         |           |

| EP20K160E  |         |         | 316     |         |           |

| EP20K200   |         |         | 382     |         |           |

| EP20K200E  |         |         | 376     | 376     |           |

| EP20K300E  |         |         |         | 408     |           |

| EP20K400   |         |         |         | 502 (3) |           |

| EP20K400E  |         |         |         | 488 (3) |           |

| EP20K600E  |         |         |         | 508 (3) | 588       |

| EP20K1000E |         |         |         | 508 (3) | 708       |

| EP20K1500E |         |         |         |         | 808       |

#### Notes to tables:

Г

- (1) I/O counts include dedicated input and clock pins.

- (2) APEX 20K device package types include thin quad flat pack (TQFP), plastic quad flat pack (PQFP), power quad flat pack (RQFP), 1.27-mm pitch ball-grid array (BGA), 1.00-mm pitch FineLine BGA, and pin-grid array (PGA) packages.

- (3) This device uses a thermally enhanced package, which is taller than the regular package. Consult the *Altera Device Package Information Data Sheet* for detailed package size information.

| Table 6. APEX 20K QFP, BGA & PGA Package Sizes                                                                                  |         |             |             |         |         |             |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|---------|-------------|-------------|---------|---------|-------------|--|--|--|--|

| Feature         144-Pin TQFP         208-Pin QFP         240-Pin QFP         356-Pin BGA         652-Pin BGA         655-Pin PC |         |             |             |         |         |             |  |  |  |  |

| Pitch (mm)                                                                                                                      | 0.50    | 0.50        | 0.50        | 1.27    | 1.27    | _           |  |  |  |  |

| Area (mm <sup>2</sup> )                                                                                                         | 484     | 924         | 1,218       | 1,225   | 2,025   | 3,906       |  |  |  |  |

| Length $\times$ Width (mm $\times$ mm)                                                                                          | 22 × 22 | 30.4 × 30.4 | 34.9 × 34.9 | 35 × 35 | 45 × 45 | 62.5 × 62.5 |  |  |  |  |

| Table 7. APEX 20K FineLine BGA Package Sizes                                              |         |       |       |         |         |  |  |  |

|-------------------------------------------------------------------------------------------|---------|-------|-------|---------|---------|--|--|--|

| Feature         144 Pin         324 Pin         484 Pin         672 Pin         1,020 Pin |         |       |       |         |         |  |  |  |

| Pitch (mm)                                                                                | 1.00    | 1.00  | 1.00  | 1.00    | 1.00    |  |  |  |

| Area (mm <sup>2</sup> )                                                                   | 169     | 361   | 529   | 729     | 1,089   |  |  |  |

| Length $	imes$ Width (mm $	imes$ mm)                                                      | 13 × 13 | 19×19 | 23×23 | 27 × 27 | 33 × 33 |  |  |  |

# General Description

APEX<sup>TM</sup> 20K devices are the first PLDs designed with the MultiCore architecture, which combines the strengths of LUT-based and productterm-based devices with an enhanced memory structure. LUT-based logic provides optimized performance and efficiency for data-path, registerintensive, mathematical, or digital signal processing (DSP) designs. Product-term-based logic is optimized for complex combinatorial paths, such as complex state machines. LUT- and product-term-based logic combined with memory functions and a wide variety of MegaCore and AMPP functions make the APEX 20K device architecture uniquely suited for system-on-a-programmable-chip designs. Applications historically requiring a combination of LUT-, product-term-, and memory-based devices can now be integrated into one APEX 20K device.

APEX 20KE devices are a superset of APEX 20K devices and include additional features such as advanced I/O standard support, CAM, additional global clocks, and enhanced ClockLock clock circuitry. In addition, APEX 20KE devices extend the APEX 20K family to over one million gates. APEX 20KE devices are denoted with an "E" suffix in the device name (e.g., the EP20K1000E device is an APEX 20KE device). Table 8 compares the features included in APEX 20K and APEX 20KE devices.

| Feature                        | APEX 20K Devices                                                                                                                                                    | APEX 20KE Devices                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MultiCore system integration   | Full support                                                                                                                                                        | Full support                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Hot-socketing support          | -                                                                                                                                                                   | Full support                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SignalTap logic analysis       | Full support                                                                                                                                                        | Full support                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 32/64-Bit, 33-MHz PCI          | Full compliance in -1, -2 speed grades                                                                                                                              | Full compliance in -1, -2 speed grades                                                                                                                                                                                                                                                                                                                                                                                                            |

| 32/64-Bit, 66-MHz PCI          | -                                                                                                                                                                   | Full compliance in -1 speed grade                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MultiVolt I/O                  | 2.5-V or 3.3-V $V_{CCIO}$<br>V <sub>CCIO</sub> selected for device<br>Certain devices are 5.0-V tolerant                                                            | 1.8-V, 2.5-V, or 3.3-V $V_{CCIO}$<br>V <sub>CCIO</sub> selected block-by-block<br>5.0-V tolerant with use of external resistor                                                                                                                                                                                                                                                                                                                    |

| ClockLock support              | Clock delay reduction<br>2× and 4× clock multiplication                                                                                                             | Clock delay reduction<br>$m/(n \times v)$ clock multiplication<br>Drive ClockLock output off-chip<br>External clock feedback<br>ClockShift<br>LVDS support<br>Up to four PLLs<br>ClockShift, clock phase adjustment                                                                                                                                                                                                                               |

| Dedicated clock and input pins | Six                                                                                                                                                                 | Eight                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I/O standard support           | 2.5-V, 3.3-V, 5.0-V I/O<br>3.3-V PCI<br>Low-voltage complementary<br>metal-oxide semiconductor<br>(LVCMOS)<br>Low-voltage transistor-to-transistor<br>logic (LVTTL) | 1.8-V, 2.5-V, 3.3-V, 5.0-V I/O<br>2.5-V I/O<br>3.3-V PCI and PCI-X<br>3.3-V Advanced Graphics Port (AGP)<br>Center tap terminated (CTT)<br>GTL+<br>LVCMOS<br>LVTTL<br>True-LVDS and LVPECL data pins<br>(in EP20K300E and larger devices)<br>LVDS and LVPECL clock pins (in all<br>devices)<br>LVDS and LVPECL data pins up to<br>156 Mbps (in -1 speed grade devices)<br>HSTL Class I<br>PCI-X<br>SSTL-2 Class I and II<br>SSTL-3 Class I and II |

| Memory support                 | Dual-port RAM<br>FIFO<br>RAM<br>ROM                                                                                                                                 | CAM<br>Dual-port RAM<br>FIFO<br>RAM<br>ROM                                                                                                                                                                                                                                                                                                                                                                                                        |

All APEX 20K devices are reconfigurable and are 100% tested prior to shipment. As a result, test vectors do not have to be generated for fault coverage purposes. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different application-specific integrated circuit (ASIC) designs; APEX 20K devices can be configured on the board for the specific functionality required.

APEX 20K devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable EPC1, EPC2, and EPC16 configuration devices, which configure APEX 20K devices via a serial data stream. Moreover, APEX 20K devices contain an optimized interface that permits microprocessors to configure APEX 20K devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat APEX 20K devices as memory and configure the device by writing to a virtual memory location, making reconfiguration easy.

After an APEX 20K device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

APEX 20K devices are supported by the Altera Quartus II development system, a single, integrated package that offers HDL and schematic design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, SignalTap logic analysis, and device configuration. The Quartus II software runs on Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations.

The Quartus II software provides NativeLink interfaces to other industrystandard PC- and UNIX workstation-based EDA tools. For example, designers can invoke the Quartus II software from within third-party design tools. Further, the Quartus II software contains built-in optimized synthesis libraries; synthesis tools can use these libraries to optimize designs for APEX 20K devices. For example, the Synopsys Design Compiler library, supplied with the Quartus II development system, includes DesignWare functions optimized for the APEX 20K architecture.

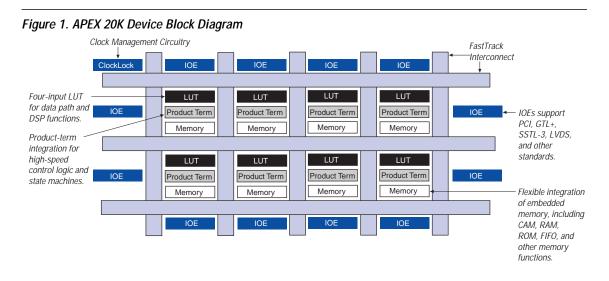

#### Functional APEX 20K devices incorporate LUT-based logic, product-term-based logic, and memory into one device. Signal interconnections within Description APEX 20K devices (as well as to and from device pins) are provided by the FastTrack Interconnect—a series of fast. continuous row and column channels that run the entire length and width of the device. Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect. Each IOE contains a bidirectional I/O buffer and a register that can be used as either an input or output register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. IOEs provide a variety of features, such as 3.3-V, 64-bit, 66-MHz PCI compliance; JTAG BST support; slew-rate control; and tri-state buffers. APEX 20KE devices offer enhanced I/O support, including support for 1.8-V I/O, 2.5-V I/O, LVCMOS, LVTTL, LVPECL, 3.3-V PCI, PCI-X, LVDS, GTL+, SSTL-2, SSTL-3, HSTL, CTT, and 3.3-V AGP I/O standards.

The ESB can implement a variety of memory functions, including CAM, RAM, dual-port RAM, ROM, and FIFO functions. Embedding the memory directly into the die improves performance and reduces die area compared to distributed-RAM implementations. Moreover, the abundance of cascadable ESBs ensures that the APEX 20K device can implement multiple wide memory blocks for high-density designs. The ESB's high speed ensures it can implement small memory blocks without any speed penalty. The abundance of ESBs ensures that designers can create as many different-sized memory blocks as the system requires. Figure 1 shows an overview of the APEX 20K device.

APEX 20K devices provide two dedicated clock pins and four dedicated input pins that drive register control inputs. These signals ensure efficient distribution of high-speed, low-skew control signals. These signals use dedicated routing channels to provide short delays and low skews. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or internally generated asynchronous clear signals with high fan-out. The dedicated clock pins featured on the APEX 20K devices can also feed logic. The devices also feature ClockLock and ClockBoost clock management circuitry. APEX 20KE devices provide two additional dedicated clock pins, for a total of four dedicated clock pins.

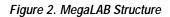

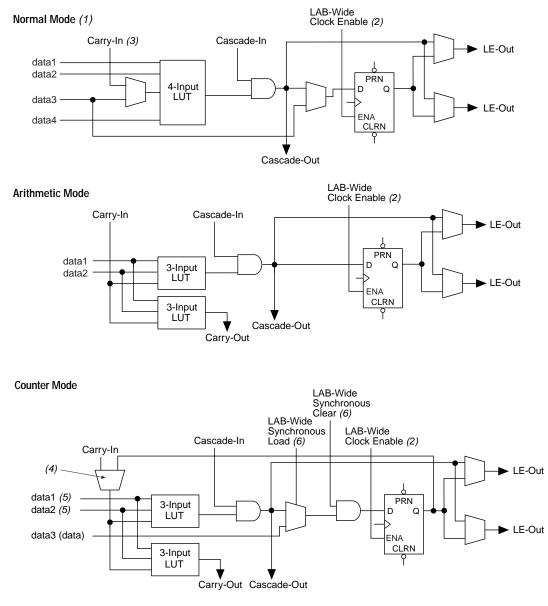

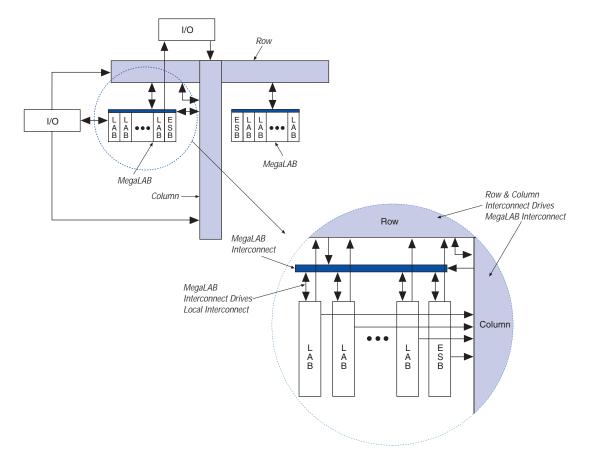

## MegaLAB Structure

APEX 20K devices are constructed from a series of MegaLAB<sup>™</sup> structures. Each MegaLAB structure contains 16 logic array blocks (LABs), one ESB, and a MegaLAB interconnect, which routes signals within the MegaLAB structure. In EP20K1000E and EP20K1500E devices, MegaLAB structures contain 24 LABs. Signals are routed between MegaLAB structures and I/O pins via the FastTrack Interconnect. In addition, edge LABs can be driven by I/O pins through the local interconnect. Figure 2 shows the MegaLAB structure.

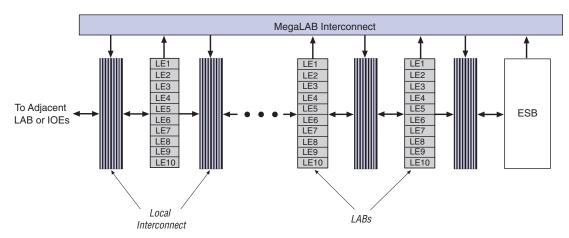

### Logic Array Block

Each LAB consists of 10 LEs, the LEs' associated carry and cascade chains, LAB control signals, and the local interconnect. The local interconnect transfers signals between LEs in the same or adjacent LABs, IOEs, or ESBs. The Quartus II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of a fast local interconnect for high performance. Figure 3 shows the APEX 20K LAB.

APEX 20K devices use an interleaved LAB structure. This structure allows each LE to drive two local interconnect areas. This feature minimizes use of the MegaLAB and FastTrack interconnect, providing higher performance and flexibility. Each LE can drive 29 other LEs through the fast local interconnect.

Each LAB contains dedicated logic for driving control signals to its LEs and ESBs. The control signals include clock, clock enable, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, and synchronous load signals. A maximum of six control signals can be used at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked (e.g., any LE in a particular LAB using CLK1 will also use CLKENA1). LEs with the same clock but different clock enable signals either use both clock signals in one LAB or are placed into separate LABs.

If both the rising and falling edges of a clock are used in an LAB, both LAB-wide clock signals are used.

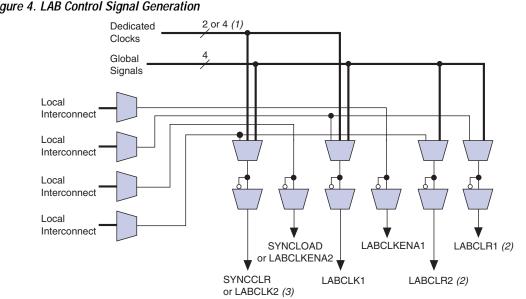

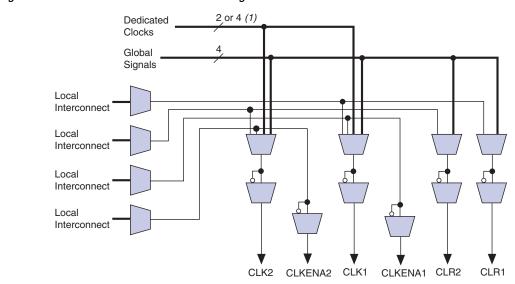

The LAB-wide control signals can be generated from the LAB local interconnect, global signals, and dedicated clock pins. The inherent low skew of the FastTrack Interconnect enables it to be used for clock distribution. Figure 4 shows the LAB control signal generation circuit.

### Figure 4. LAB Control Signal Generation

### Notes:

- APEX 20KE devices have four dedicated clocks. (1)

- (2) The LABCLR1 and LABCLR2 signals also control asynchronous load and asynchronous preset for LEs within the LAB.

- The SYNCCLR signal can be generated by the local interconnect or global signals. (3)

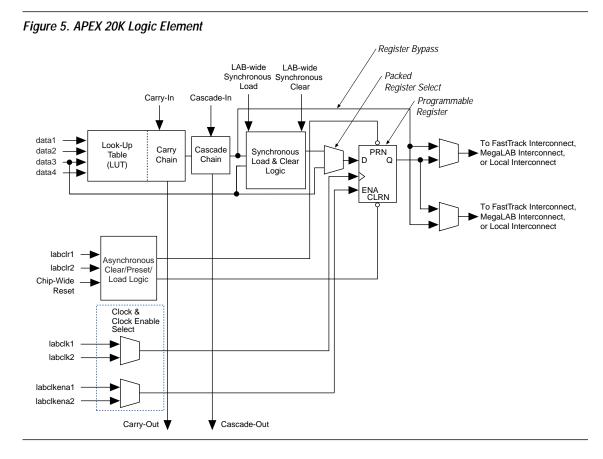

### Logic Element

The LE, the smallest unit of logic in the APEX 20K architecture, is compact and provides efficient logic usage. Each LE contains a four-input LUT, which is a function generator that can quickly implement any function of four variables. In addition, each LE contains a programmable register and carry and cascade chains. Each LE drives the local interconnect, MegaLAB interconnect, and FastTrack Interconnect routing structures. See Figure 5.

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives the outputs of the LE.

Each LE has two outputs that drive the local, MegaLAB, or FastTrack Interconnect routing structure. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

The APEX 20K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. A carry chain supports high-speed arithmetic functions such as counters and adders, while a cascade chain implements wide-input functions such as equality comparators with minimum delay. Carry and cascade chains connect LEs 1 through 10 in an LAB and all LABs in the same MegaLAB structure.

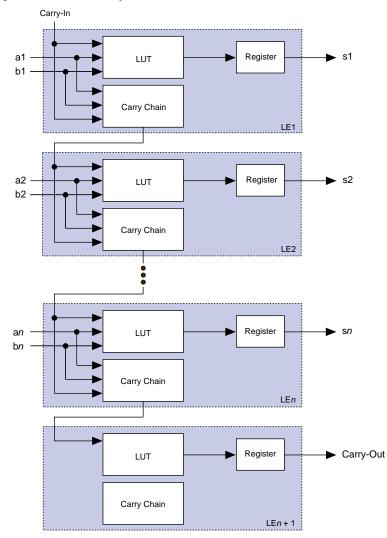

### Carry Chain

The carry chain provides a very fast carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higherorder bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the APEX 20K architecture to implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as library of parameterized modules (LPM) and DesignWare functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II software Compiler creates carry chains longer than ten LEs by linking LABs together automatically. For enhanced fitting, a long carry chain skips alternate LABs in a MegaLAB structure. A carry chain longer than one LAB skips either from an even-numbered LAB to the next evennumbered LAB, or from an odd-numbered LAB to the next oddnumbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure.

Figure 6 shows how an *n*-bit full adder can be implemented in n + 1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven onto the local, MegaLAB, or FastTrack Interconnect routing structures.

Figure 6. APEX 20K Carry Chain

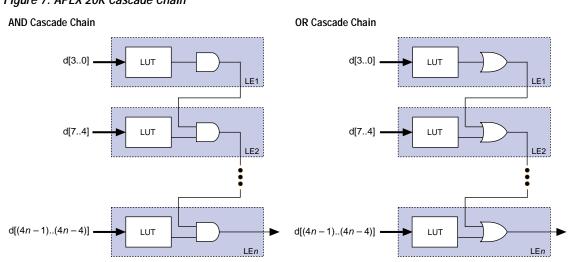

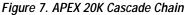

### Cascade Chain

With the cascade chain, the APEX 20K architecture can implement functions with a very wide fan-in. Adjacent LUTs can compute portions of a function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a short cascade delay. Cascade chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than ten LEs are implemented automatically by linking LABs together. For enhanced fitting, a long cascade chain skips alternate LABs in a MegaLAB structure. A cascade chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure. Figure 7 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in.

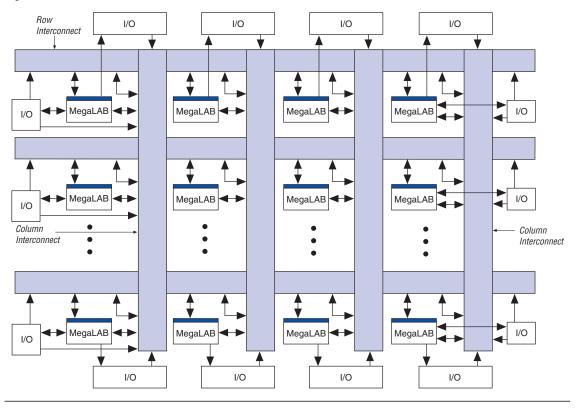

### LE Operating Modes

The APEX 20K LE can operate in one of the following three modes:

- Normal mode

- Arithmetic mode

- Counter mode

Each mode uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes.

The Quartus II software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions that specify which LE operating mode to use for optimal performance. Figure 8 shows the LE operating modes.

### Figure 8. APEX 20K LE Operating Modes

#### Notes:

- (1) LEs in normal mode support register packing.

- (2) There are two LAB-wide clock enables per LAB.

- (3) When using the carry-in in normal mode, the packed register feature is unavailable.

- (4) A register feedback multiplexer is available on LE1 of each LAB.

- (5) The DATA1 and DATA2 input signals can supply counter enable, up or down control, or register feedback signals for LEs other than the second LE in an LAB.

- (6) The LAB-wide synchronous clear and LAB wide synchronous load affect all registers in an LAB.

#### Normal Mode

The normal mode is suitable for general logic applications, combinatorial functions, or wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Quartus II software Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. LEs in normal mode support packed registers.

#### **Arithmetic Mode**

The arithmetic mode is ideal for implementing adders, accumulators, and comparators. An LE in arithmetic mode uses two 3-input LUTs. One LUT computes a three-input function; the other generates a carry output. As shown in Figure 8, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, when implementing an adder, this output is the sum of three signals: DATA1, DATA2, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The Quartus II software implements parameterized functions that use the arithmetic mode automatically where appropriate; the designer does not need to specify how the carry chain will be used.

#### **Counter Mode**

The counter mode offers clock enable, counter enable, synchronous up/down control, synchronous clear, and synchronous load options. The counter enable and synchronous up/down control signals are generated from the data inputs of the LAB local interconnect. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. Consequently, if any of the LEs in an LAB use the counter mode, other LEs in that LAB must be used as part of the same counter or be used for a combinatorial function. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

The counter mode uses two three-input LUTs: one generates the counter data, and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading, and another AND gate provides synchronous clearing. If the cascade function is used by an LE in counter mode, the synchronous clear or load overrides any signal carried on the cascade chain. The synchronous clear overrides the synchronous load. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

### Clear & Preset Logic Control

Logic for the register's clear and preset signals is controlled by LAB-wide signals. The LE directly supports an asynchronous clear function. The Quartus II software Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset. Moreover, the Quartus II software Compiler can use a programmable NOT-gate push-back technique to emulate simultaneous preset and clear or asynchronous load. However, this technique uses three additional LEs per register. All emulation is performed automatically when the design is compiled. Registers that emulate simultaneous preset and load will enter an unknown state upon power-up or when the chip-wide reset is asserted.

In addition to the two clear and preset modes, APEX 20K devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. Use of this pin is controlled through an option in the Quartus II software that is set before compilation. The chip-wide reset overrides all other control signals. Registers using an asynchronous preset are preset when the chip-wide reset is asserted; this effect results from the inversion technique used to implement the asynchronous preset.

### FastTrack Interconnect

In the APEX 20K architecture, connections between LEs, ESBs, and I/O pins are provided by the FastTrack Interconnect. The FastTrack Interconnect is a series of continuous horizontal and vertical routing channels that traverse the device. This global routing structure provides predictable performance, even in complex designs. In contrast, the segmented routing in FPGAs requires switch matrices to connect a variable number of routing paths, increasing the delays between logic resources and reducing performance.

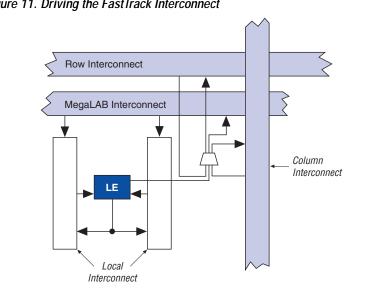

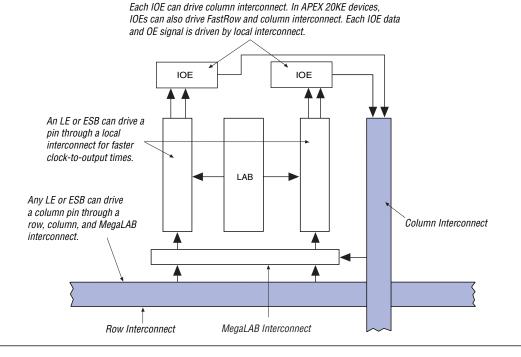

The FastTrack Interconnect consists of row and column interconnect channels that span the entire device. The row interconnect routes signals throughout a row of MegaLAB structures; the column interconnect routes signals throughout a column of MegaLAB structures. When using the row and column interconnect, an LE, IOE, or ESB can drive any other LE, IOE, or ESB in a device. See Figure 9.

Figure 9. APEX 20K Interconnect Structure

A row line can be driven directly by LEs, IOEs, or ESBs in that row. Further, a column line can drive a row line, allowing an LE, IOE, or ESB to drive elements in a different row via the column and row interconnect. The row interconnect drives the MegaLAB interconnect to drive LEs, IOEs, or ESBs in a particular MegaLAB structure.

A column line can be directly driven by LEs, IOEs, or ESBs in that column. A column line on a device's left or right edge can also be driven by row IOEs. The column line is used to route signals from one row to another. A column line can drive a row line; it can also drive the MegaLAB interconnect directly, allowing faster connections between rows.

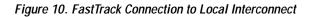

Figure 10 shows how the FastTrack Interconnect uses the local interconnect to drive LEs within MegaLAB structures.

Figure 11 shows the intersection of a row and column interconnect, and how these forms of interconnects and LEs drive each other.

Figure 11. Driving the FastTrack Interconnect

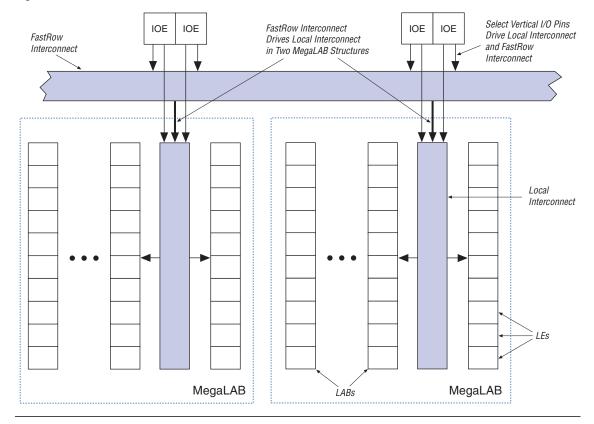

APEX 20KE devices include an enhanced interconnect structure for faster routing of input signals with high fan-out. Column I/O pins can drive the FastRow interconnect, which routes signals directly into the local interconnect without having to drive through the MegaLAB interconnect. FastRow lines traverse two MegaLAB structures. Also, these pins can drive the local interconnect directly for fast setup times. On EP20K300E and larger devices, the FastRow interconnect drives the two MegaLABs in the top left corner and the two MegaLABs in the bottom right corner. On EP20K200E and smaller devices, FastRow interconnect drives the two MegaLABs on the top and the two MegaLABs on the bottom of the device. On all devices, the FastRow interconnect drives all local interconnect in the appropriate MegaLABs except the interconnect areas on the far left and far right of the MegaLAB. Pins using the FastRow interconnect achieve a faster set-up time, as the signal does not need to use a MegaLab interconnect line to reach the destination LE. Figure 12 shows the FastRow interconnect.

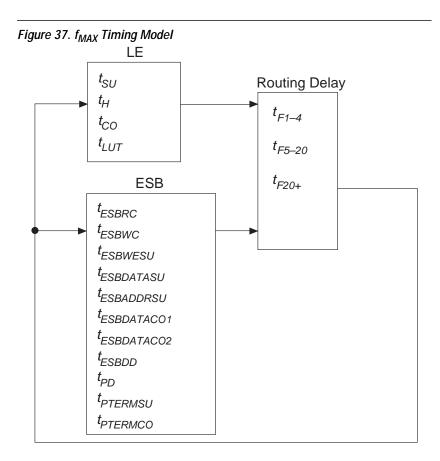

Table 9 summarizes how various elements of the APEX 20K architecture drive each other.

| Table 9. APEX 20K Routing Scheme    |                |                   |    |     |                                 |                         |                                  |                                     |                         |

|-------------------------------------|----------------|-------------------|----|-----|---------------------------------|-------------------------|----------------------------------|-------------------------------------|-------------------------|

| Source                              | Destination    |                   |    |     |                                 |                         |                                  |                                     |                         |

|                                     | Row<br>I/O Pin | Column<br>I/O Pin | LE | ESB | Local<br>Interconnect           | MegaLAB<br>Interconnect | Row<br>FastTrack<br>Interconnect | Column<br>FastTrack<br>Interconnect | FastRow<br>Interconnect |

| Row I/O Pin                         |                |                   |    |     | $\checkmark$                    | $\checkmark$            | $\checkmark$                     | $\checkmark$                        |                         |

| Column I/O<br>Pin                   |                |                   |    |     | <ul><li>✓</li><li>(1)</li></ul> |                         |                                  | ~                                   | ✓<br>(1)                |

| LE                                  |                |                   |    |     | $\checkmark$                    | $\checkmark$            | $\checkmark$                     | $\checkmark$                        |                         |

| ESB                                 |                |                   |    |     | $\checkmark$                    | $\checkmark$            | $\checkmark$                     | $\checkmark$                        |                         |

| Local<br>Interconnect               | ~              | ~                 | ~  | ~   |                                 |                         |                                  |                                     |                         |

| MegaLAB<br>Interconnect             |                |                   |    |     | ~                               |                         |                                  |                                     |                         |

| Row<br>FastTrack<br>Interconnect    |                |                   |    |     |                                 | $\checkmark$            |                                  | $\checkmark$                        |                         |

| Column<br>FastTrack<br>Interconnect |                |                   |    |     |                                 | ~                       | ~                                |                                     |                         |

| FastRow<br>Interconnect             |                |                   |    |     | <ul><li>✓</li><li>(1)</li></ul> |                         |                                  |                                     |                         |

#### Note:

(1) This connection is supported in APEX 20KE devices only.

### **Product-Term Logic**

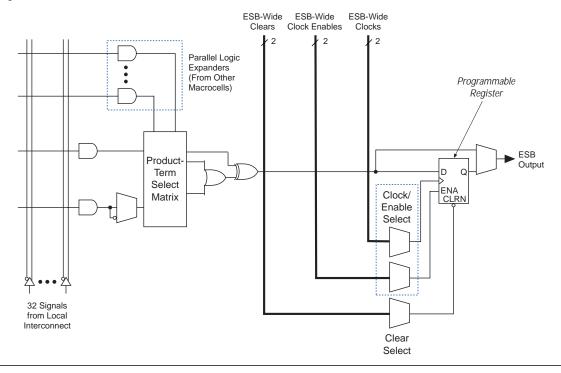

The product-term portion of the MultiCore architecture is implemented with the ESB. The ESB can be configured to act as a block of macrocells on an ESB-by-ESB basis. Each ESB is fed by 32 inputs from the adjacent local interconnect; therefore, it can be driven by the MegaLAB interconnect or the adjacent LAB. Also, nine ESB macrocells feed back into the ESB through the local interconnect for higher performance. Dedicated clock pins, global signals, and additional inputs from the local interconnect drive the ESB control signals.

In product-term mode, each ESB contains 16 macrocells. Each macrocell consists of two product terms and a programmable register. Figure 13 shows the ESB in product-term mode.

### Figure 13. Product-Term Logic in ESB

### (1) APEX 20KE devices have four dedicated clocks.

### Macrocells

APEX 20K macrocells can be configured individually for either sequential or combinatorial logic operation. The macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register.

Combinatorial logic is implemented in the product terms. The productterm select matrix allocates these product terms for use as either primary logic inputs (to the OR and XOR gates) to implement combinatorial functions, or as parallel expanders to be used to increase the logic available to another macrocell. One product term can be inverted; the Quartus II software uses this feature to perform DeMorgan's inversion for more efficient implementation of wide OR functions. The Quartus II software Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset. Figure 14 shows the APEX 20K macrocell.

#### Figure 14. APEX 20K Macrocell

For registered functions, each macrocell register can be programmed individually to implement D, T, JK, or SR operation with programmable clock control. The register can be bypassed for combinatorial operation. During design entry, the designer specifies the desired register type; the Quartus II software then selects the most efficient register operation for each registered function to optimize resource utilization. The Quartus II software or other synthesis tools can also select the most efficient register operation automatically when synthesizing HDL designs.

Each programmable register can be clocked by one of two ESB-wide clocks. The ESB-wide clocks can be generated from device dedicated clock pins, global signals, or local interconnect. Each clock also has an associated clock enable, generated from the local interconnect. The clock and clock enable signals are related for a particular ESB; any macrocell using a clock also uses the associated clock enable.

If both the rising and falling edges of a clock are used in an ESB, both ESB-wide clock signals are used.

The programmable register also supports an asynchronous clear function. Within the ESB, two asynchronous clears are generated from global signals and the local interconnect. Each macrocell can either choose between the two asynchronous clear signals or choose to not be cleared. Either of the two clear signals can be inverted within the ESB. Figure 15 shows the ESB control logic when implementing product-terms.

#### Figure 15. ESB Product-Term Mode Control Logic

#### Note:

(1) APEX 20KE devices have four dedicated clocks.

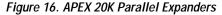

#### Parallel Expanders

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 32 product terms to feed the macrocell OR logic directly, with two product terms provided by the macrocell and 30 parallel expanders provided by the neighboring macrocells in the ESB.

The Quartus II software Compiler can allocate up to 15 sets of up to two parallel expanders per set to the macrocells automatically. Each set of two parallel expanders incurs a small, incremental timing delay. Figure 16 shows the APEX 20K parallel expanders.

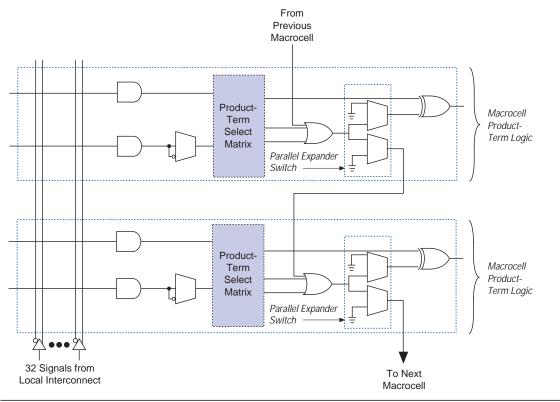

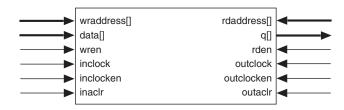

# Embedded System Block

The ESB can implement various types of memory blocks, including dual-port RAM, ROM, FIFO, and CAM blocks. The ESB includes input and output registers; the input registers synchronize writes, and the output registers can pipeline designs to improve system performance. The ESB offers a dual-port mode, which supports simultaneous reads and writes at two different clock frequencies. Figure 17 shows the ESB block diagram.

#### Figure 17. ESB Block Diagram

ESBs can implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable (WE) signal, while ensuring that its data and address signals meet setup and hold time specifications relative to the WE signal. In contrast, the ESB's synchronous RAM generates its own WE signal and is self-timed with respect to the global clock. Circuits using the ESB's selftimed RAM must only meet the setup and hold time specifications of the global clock.

ESB inputs are driven by the adjacent local interconnect, which in turn can be driven by the MegaLAB or FastTrack Interconnect. Because the ESB can be driven by the local interconnect, an adjacent LE can drive it directly for fast memory access. ESB outputs drive the MegaLAB and FastTrack Interconnect. In addition, ten ESB outputs, nine of which are unique output lines, drive the local interconnect for fast connection to adjacent LEs or for fast feedback product-term logic.

When implementing memory, each ESB can be configured in any of the following sizes:  $128 \times 16$ ,  $256 \times 8$ ,  $512 \times 4$ ,  $1,024 \times 2$ , or  $2,048 \times 1$ . By combining multiple ESBs, the Quartus II software implements larger memory blocks automatically. For example, two  $128 \times 16$  RAM blocks can be combined to form a  $128 \times 32$  RAM block, and two  $512 \times 4$  RAM blocks can be combined to form a  $512 \times 8$  RAM block. Memory performance does not degrade for memory blocks up to 2,048 words deep. Each ESB can implement a 2,048-word-deep memory; the ESBs are used in parallel, eliminating the need for any external control logic and its associated delays.

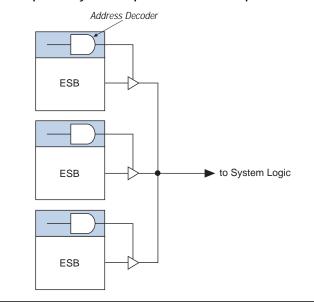

To create a high-speed memory block that is more than 2,048 words deep, ESBs drive tri-state lines. Each tri-state line connects all ESBs in a column of MegaLAB structures, and drives the MegaLAB interconnect and row and column FastTrack Interconnect throughout the column. Each ESB incorporates a programmable decoder to activate the tri-state driver appropriately. For instance, to implement 8,192-word-deep memory, four ESBs are used. Eleven address lines drive the ESB memory, and two more drive the tri-state decoder. Depending on which 2,048-word memory page is selected, the appropriate ESB driver is turned on, driving the output to the tri-state line. The Quartus II software automatically combines ESBs with tri-state lines to form deeper memory blocks. The internal tri-state control logic is designed to avoid internal contention and floating lines. See Figure 18.

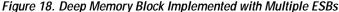

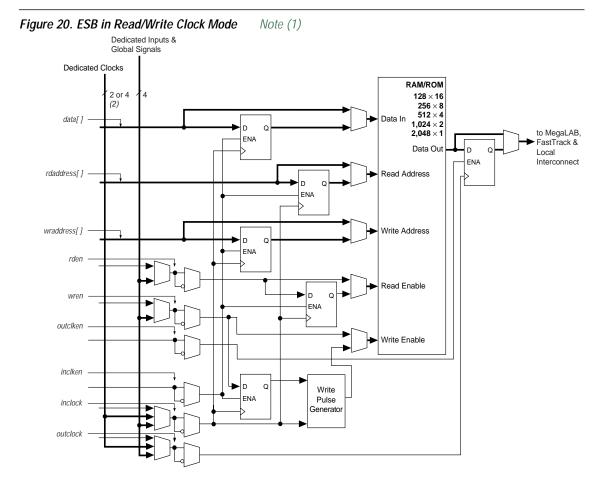

The ESB implements two forms of dual-port memory: read/write clock mode and input/output clock mode. The ESB can also be used for bidirectional, dual-port memory applications in which two ports read or write simultaneously. To implement this type of dual-port memory, two or four ESBs are used to support two simultaneous reads or writes. This functionality is shown in Figure 19.

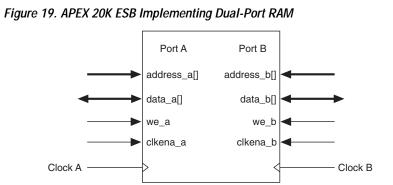

### Read/Write Clock Mode

The read/write clock mode contains two clocks. One clock controls all registers associated with writing: data input, WE, and write address. The other clock controls all registers associated with reading: read enable (RE), read address, and data output. The ESB also supports clock enable and asynchronous clear signals; these signals also control the read and write registers independently. Read/write clock mode is commonly used for applications where reads and writes occur at different system frequencies. Figure 20 shows the ESB in read/write clock mode.

#### Notes:

- (1) All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset.

- (2) APEX 20KE devices have four dedicated clocks.

### Input/Output Clock Mode

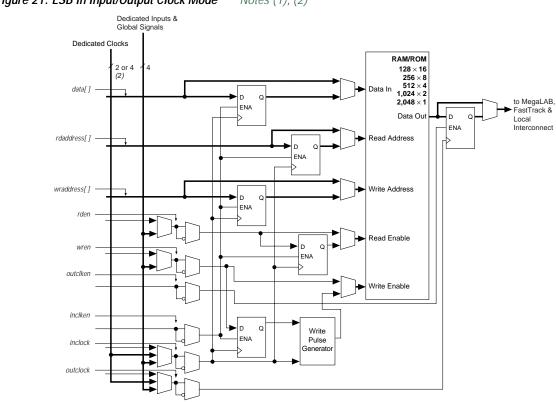

The input/output clock mode contains two clocks. One clock controls all registers for inputs into the ESB: data input, WE, RE, read address, and write address. The other clock controls the ESB data output registers. The ESB also supports clock enable and asynchronous clear signals; these signals also control the reading and writing of registers independently. Input/output clock mode is commonly used for applications where the reads and writes occur at the same system frequency, but require different clock enable signals for the input and output registers. Figure 21 shows the ESB in input/output clock mode.

#### Figure 21. ESB in Input/Output Clock Mode Notes (1), (2)

#### Notes:

- (1)All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset.

- APEX 20KE devices have four dedicated clocks. (2)

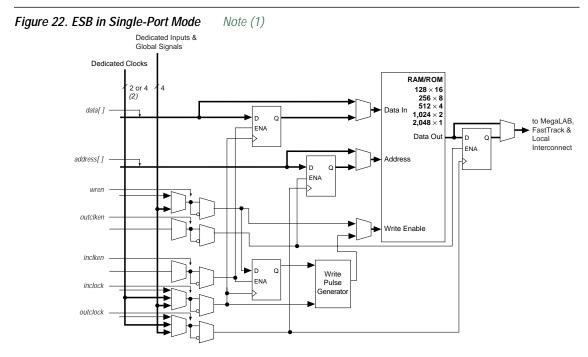

### Single-Port Mode

The APEX 20K ESB also supports a single-port mode, which is used when simultaneous reads and writes are not required. See Figure 22.

#### Notes:

- (1) All registers can be asynchronously cleared by ESB local interconnect signals, global signals, or the chip-wide reset.

- (2) APEX 20KE devices have four dedicated clocks.

### **Content-Addressable Memory**

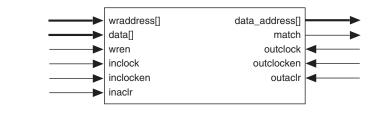

In APEX 20KE devices, the ESB can implement CAM. CAM can be thought of as the inverse of RAM. When read, RAM outputs the data for a given address. Conversely, CAM outputs an address for a given data word. For example, if the data FA12 is stored in address 14, the CAM outputs 14 when FA12 is driven into it.

CAM is used for high-speed search operations. When searching for data within a RAM block, the search is performed serially. Thus, finding a particular data word can take many cycles. CAM searches all addresses in parallel and outputs the address storing a particular word. When a match is found, a match flag is set high. Figure 23 shows the CAM block diagram.

Figure 23. APEX 20KE CAM Block Diagram

CAM can be used in any application requiring high-speed searches, such as networking, communications, data compression, and cache management.

The APEX 20KE on-chip CAM provides faster system performance than traditional discrete CAM. Integrating CAM and logic into the APEX 20KE device eliminates off-chip and on-chip delays, improving system performance.

When in CAM mode, the ESB implements 32-word, 32-bit CAM. Wider or deeper CAM can be implemented by combining multiple CAMs with some ancillary logic implemented in LEs. The Quartus II software combines ESBs and LEs automatically to create larger CAMs.

CAM supports writing "don't care" bits into words of the memory. The "don't-care" bit can be used as a mask for CAM comparisons; any bit set to "don't-care" has no effect on matches.

The output of the CAM can be encoded or unencoded. When encoded, the ESB outputs an encoded address of the data's location. For instance, if the data is located in address 12, the ESB output is 12. When unencoded, the ESB uses its 16 outputs to show the location of the data over two clock cycles. In this case, if the data is located in address 12, the 12th output line goes high. When using unencoded outputs, two clock cycles are required to read the output because a 16-bit output bus is used to show the status of 32 words.

The encoded output is better suited for designs that ensure duplicate data is not written into the CAM. If duplicate data is written into two locations, the CAM's output will be incorrect. If the CAM may contain duplicate data, the unencoded output is a better solution; CAM with unencoded outputs can distinguish multiple data locations.

CAM can be pre-loaded with data during configuration, or it can be written during system operation. In most cases, two clock cycles are required to write each word into CAM. When "don't-care" bits are used, a third clock cycle is required.

For more information on APEX 20KE devices and CAM, see Application Note 119 (Implementing High-Speed Search Applications with APEX CAM).

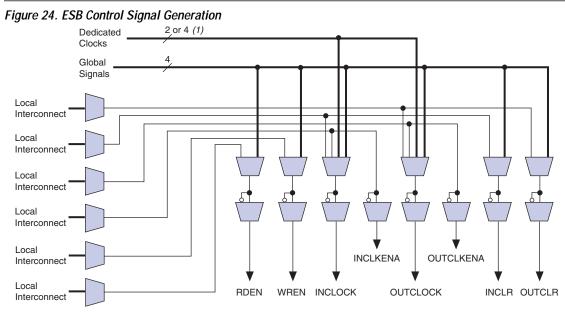

### Driving Signals to the ESB

ESBs provide flexible options for driving control signals. Different clocks can be used for the ESB inputs and outputs. Registers can be inserted independently on the data input, data output, read address, write address, WE, and RE signals. The global signals and the local interconnect can drive the WE and RE signals. The global signals, dedicated clock pins, and local interconnect can drive the ESB clock signals. Because the LEs drive the local interconnect, the LEs can control the WE and RE signals and the ESB clock, clock enable, and asynchronous clear signals. Figure 24 shows the ESB control signal generation logic.

#### Note:

(1) APEX 20KE devices have four dedicated clocks.

An ESB is fed by the local interconnect, which is driven by adjacent LEs (for high-speed connection to the ESB) or the MegaLAB interconnect. The ESB can drive the local, MegaLAB, or FastTrack Interconnect routing structure to drive LEs and IOEs in the same MegaLAB structure or anywhere in the device.

### Implementing Logic in ROM

In addition to implementing logic with product terms, the ESB can implement logic functions when it is programmed with a read-only pattern during configuration, creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results, rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of ESBs. The large capacity of ESBs enables designers to implement complex functions in one logic level without the routing delays associated with linked LEs or distributed RAM blocks. Parameterized functions such as LPM functions can take advantage of the ESB automatically. Further, the Quartus II software can implement portions of a design with ESBs where appropriate.

#### Programmable Speed/Power Control

APEX 20K ESBs offer a high-speed mode that supports very fast operation on an ESB-by-ESB basis. When high speed is not required, this feature can be turned off to reduce the ESB's power dissipation by up to 50%. ESBs that run at low power incur a nominal timing delay adder. This Turbo Bit<sup>™</sup> option is available for ESBs that implement product-term logic or memory functions. An ESB that is not used will be powered down so that it does not consume DC current.

Designers can program each ESB in the APEX 20K device for either high-speed or low-power operation. As a result, speed-critical paths in the design can run at high speed, while the remaining paths operate at reduced power.

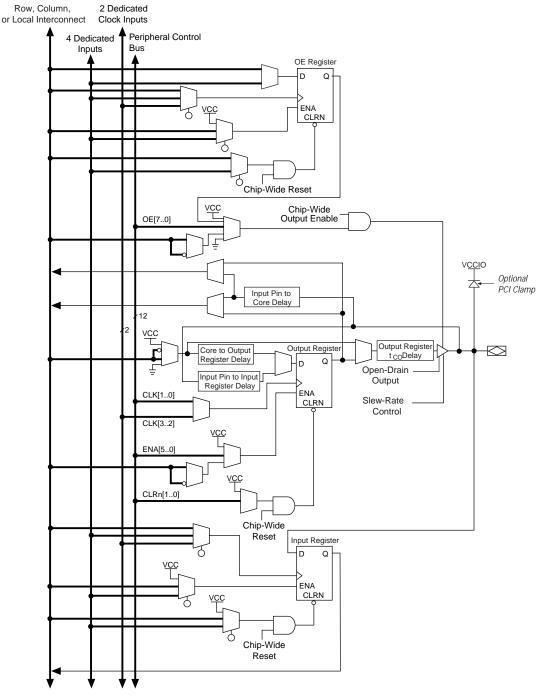

## I/O Structure

The APEX 20K IOE contains a bidirectional I/O buffer and a register that can be used either as an input register for external data requiring fast setup times, or as an output register for data requiring fast clock-to-output performance. IOEs can be used as input, output, or bidirectional pins. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing. The Quartus II software Compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. Because the APEX 20K IOE offers one output enable per pin, the Quartus II software Compiler can emulate open-drain operation efficiently.

The APEX 20K IOE includes programmable delays that can be activated to ensure zero hold times, minimum clock-to-output times, input IOE register-to-core register transfers, or core-to-output IOE register transfers. A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Table 10 describes the APEX 20K programmable delays and their logic options in the Quartus II software.

| Table 10 AP | EX 20K Programma | ble Delav Chains |

|-------------|------------------|------------------|

| 10010 10.70 |                  |                  |

| Programmable Delays                         | Quartus II Logic Option                 |

|---------------------------------------------|-----------------------------------------|

| Input pin to core delay                     | Decrease input delay to internal cells  |

| Input pin to input register delay           | Decrease input delay to input register  |

| Core to output register delay               | Decrease input delay to output register |

| Output register <b>t<sub>CO</sub></b> delay | Increase delay to output pin            |

The Quartus II software Compiler can program these delays automatically to minimize setup time while providing a zero hold time. Figure 25 shows how fast bidirectional I/Os are implemented in APEX 20K devices.

The register in the APEX 20K IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, the register cannot be asynchronously cleared or preset. This feature is useful for cases where the APEX 20K device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up.

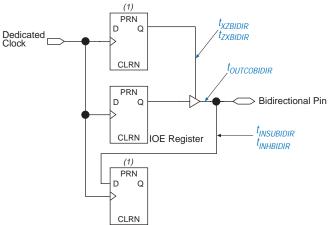

#### Figure 25. APEX 20K Bidirectional I/O Registers Note (1)

#### Note:

(1) The output enable and input registers are LE registers in the LAB adjacent to the bidirectional pin.

#### Altera Corporation

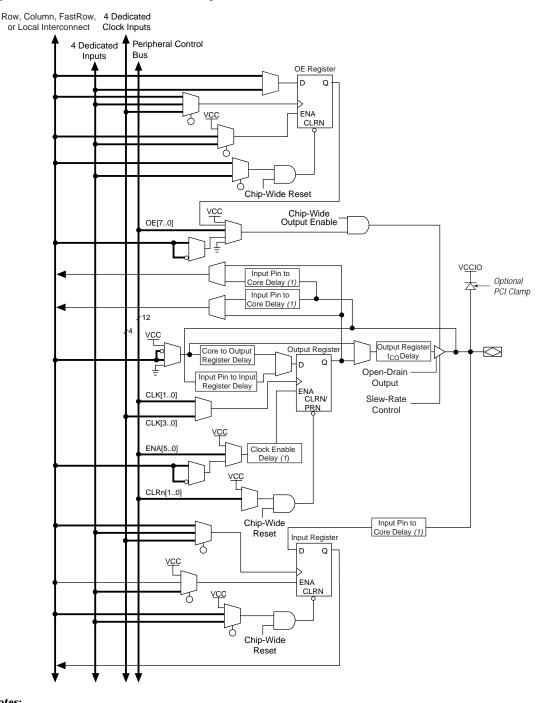

APEX 20KE devices include an enhanced IOE, which drives the FastRow interconnect. The FastRow interconnect connects a column I/O pin directly to the LAB local interconnect within two MegaLAB structures. This feature provides fast setup times for pins that drive high fan-outs with complex logic, such as PCI designs. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing. The APEX 20KE IOE also includes direct support for open-drain operation, giving faster clock-to-output for open-drain signals. Some programmable delays in the APEX 20KE IOE offer multiple levels of delay to fine-tune setup and hold time requirements. The Quartus II software Compiler can set these delays automatically to minimize setup time while providing a zero hold time.

Table 11 describes the APEX 20KE programmable delays and their logic options in the Quartus II software.

| Table 11. APEX 20KE Programmable Delay Chains |                                         |  |  |

|-----------------------------------------------|-----------------------------------------|--|--|

| Programmable Delays                           | Quartus II Logic Option                 |  |  |

| Input Pin to Core Delay                       | Decrease input delay to internal cells  |  |  |

| Input Pin to Input Register Delay             | Decrease input delay to input registers |  |  |

| Core to Output Register Delay                 | Decrease input delay to output register |  |  |

| Output Register t <sub>CO</sub> Delay         | Increase delay to output pin            |  |  |

| Clock Enable Delay                            | Increase clock enable delay             |  |  |

The register in the APEX 20KE IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, an asynchronous preset can control the register. Figure 26 shows how fast bidirectional I/O pins are implemented in APEX 20KE devices. This feature is useful for cases where the APEX 20KE device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up.

#### Figure 26. APEX 20KE Bidirectional I/O Registers

Notes (1), (2)

#### Notes:

- (1) This programmable delay has four settings: off and three levels of delay.

- (2) The output enable and input registers are LE registers in the LAB adjacent to the bidirectional pin.

#### Altera Corporation

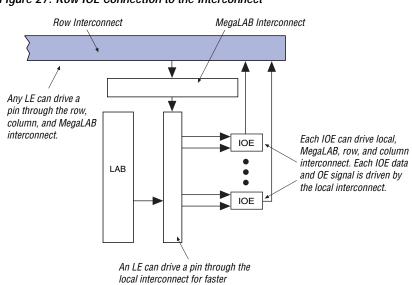

Each IOE drives a row, column, MegaLAB, or local interconnect when used as an input or bidirectional pin. A row IOE can drive a local, MegaLAB, row, and column interconnect; a column IOE can drive the column interconnect. Figure 27 shows how a row IOE connects to the interconnect.

clock-to-output times.

Figure 28 shows how a column IOE connects to the interconnect.

#### Figure 28. Column IOE Connection to the Interconnect

### **Dedicated Fast I/O Pins**

APEX 20KE devices incorporate an enhancement to support bidirectional pins with high internal fanout such as PCI control signals. These pins are called Dedicated Fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and replace dedicated inputs. These pins can be used for fast clock, clear, or high fanout logic signal distribution. They also can drive out. The Dedicated Fast I/O pin data output and tri-state control are driven by local interconnect from the adjacent MegaLAB for high speed.

#### Advanced I/O Standard Support

APEX 20KE IOEs support the following I/O standards: LVTTL, LVCMOS, 1.8-V I/O, 2.5-V I/O, 3.3-V PCI, PCI-X, 3.3-V AGP, LVDS, LVPECL, GTL+, CTT, HSTL Class I, SSTL-3 Class I and II, and SSTL-2 Class I and II.

For more information on I/O standards supported by APEX 20KE devices, see *Application Note 117 (Using Selectable I/O Standards in Altera Devices)*.

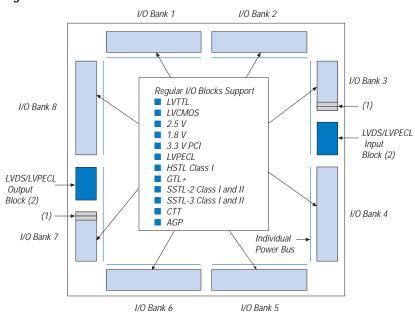

The APEX 20KE device contains eight I/O banks. In QFP packages, the banks are linked to form four I/O banks. The I/O banks directly support all standards except LVDS and LVPECL. All I/O banks can support LVDS and LVPECL with the addition of external resistors. In addition, one block within a bank contains circuitry to support high-speed True-LVDS and LVPECL inputs, and another block within a particular bank supports high-speed True-LVDS and LVPECL outputs. The LVDS blocks support all of the I/O standards. Each I/O bank has its own VCCIO pins. A single device can support 1.8-V, 2.5-V, and 3.3-V interfaces; each bank can support a different standard independently. Each bank can also use a separate V<sub>REF</sub> level so that each bank can support any of the terminated standards (such as SSTL-3) independently. Within a bank, any one of the terminated standards can be supported. EP20K300E and larger APEX 20KE devices support the LVDS interface for data pins (smaller devices support LVDS clock pins, but not data pins). All EP20K300E and larger devices support the LVDS interface for data pins up to 155 Mbit per channel; EP20K400E devices and larger with an X-suffix on the ordering code add a serializer/deserializer circuit and PLL for higher-speed support.

Each bank can support multiple standards with the same VCCIO for output pins. Each bank can support one voltage-referenced I/O standard, but it can support multiple I/O standards with the same VCCIO voltage level. For example, when VCCIO is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

When the LVDS banks are not used as LVDS I/O banks, they support all of the other I/O standards. Figure 29 shows the arrangement of the APEX 20KE I/O banks.

Figure 29. APEX 20KE I/O Banks

#### Notes:

- The first two I/O pins that border the LVDS blocks can only be used for input to maintain an acceptable noise level on the V<sub>CCIO</sub> plane.

- (2) If the LVDS input and output blocks are not used for LVDS, they can support all of the I/O standards and can be used as input, output, or bidirectional pins with  $V_{CCIO}$  set to 3.3 V, 2.5 V, or 1.8 V.

### Power Sequencing & Hot Socketing

Because APEX 20K devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{CCIO}$  and  $V_{CCINT}$  power supplies may be powered in any order.

Signals can be driven into APEX 20K devices before and during power-up without damaging the device. In addition, APEX 20K devices do not drive out during power-up. Once operating conditions are reached and the device is configured, APEX 20K devices operate as specified by the user.

MultiVolt I/O<br/>InterfaceThe APEX device architecture supports the MultiVolt I/O interface<br/>feature, which allows APEX devices in all packages to interface with<br/>systems of different supply voltages. The devices have one set of VCC pins<br/>for internal operation and input buffers (VCCINT), and another set for I/O<br/>output drivers (VCCIO).

The APEX 20K VCCINT pins must always be connected to a 2.5 V power supply. With a 2.5-V V<sub>CCINT</sub> level, input pins are 2.5-V and 3.3-V tolerant. Certain devices, identified by a "V" suffix following the speed grade in the ordering code (e.g., EP20K400BC652-1V), are 5.0-V tolerant. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

Table 12 summarizes 5.0-V tolerant APEX 20K MultiVolt I/O support.

| Table 12. 5.0-V Tolerant APEX 20K MultiVolt I/O Support |              |                                      |           |              |              |              |

|---------------------------------------------------------|--------------|--------------------------------------|-----------|--------------|--------------|--------------|

| V <sub>CCIO</sub> (V)                                   | In           | Input Signals (V) Output Signals (V) |           |              | (V)          |              |

|                                                         | 2.5          | 3.3                                  | 5.0       | 2.5          | 3.3          | 5.0          |

| 2.5                                                     | $\checkmark$ | ✓(1)                                 | √(1), (2) | $\checkmark$ |              |              |

| 3.3                                                     | $\checkmark$ | $\checkmark$                         | √(1), (2) | ✓ (3)        | $\checkmark$ | $\checkmark$ |

#### Notes:

- (1) The PCI clamping diode must be disabled to drive an input with voltages higher than  $V_{\mbox{\scriptsize CCIO}}.$

- (2) APEX 20K devices with a "V" suffix are 5.0-V tolerant.

- (3) When  $V_{CCIO} = 3.3$  V, an APEX 20K device can drive a 2.5-V device with 3.3-V tolerant inputs.